## МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего образования

«Воронежский государственный технический университет»

УТВЕРЖДАЮ Декан факультета /В.А. Небольсин/

31 августа 2021 г.

# РАБОЧАЯ ПРОГРАММА

дисциплины

#### «Интегральные устройства радиоэлектроники»

**Направление подготовки** <u>11.03.03 Конструирование и технология</u> электронных средств

Профиль Проектирование и технология радиоэлектронных средств

Квалификация выпускника бакалавр

Нормативный период обучения 4 года / 4 года 11 месяцев

Форма обучения Очная / Заочная

Год начала подготовки 2020

Автор программы

А.А. Пирогов

Заведующий кафедрой

А.В. Башкиров

Руководитель ОПОП

А.А. Пирогов

Воронеж 2021

#### 1 ЦЕЛИ И ЗАДАЧИ ДИСЦИПЛИНЫ

**1.1 Цели дисциплины:** изучение принципов работы, материалов, конструкций и технологических процессов изготовления интегральных устройств электроники, освоение методик проектирования интегральных устройств электроники.

#### 1.2 Задачи освоения дисциплины:

- теоретическое изучение устройства аналоговых интегральных структур, физических принципов работы, характеристик и особенностей их применения в производстве РЭС;

- изучение назначения и принципов действия основных устройств интегральной электроники;

- приобретение навыков проектирования РЭС с применением современных САПР.

#### 2 МЕСТО ДИСЦИПЛИНЫ В СТРУКТУРЕ ОПОП

Дисциплина <u>«Интегральные устройства радиоэлектроники»</u> относится к дисциплинам обязательной части блока Б.1 учебного плана.

#### 3 ПЕРЕЧЕНЬ ПЛАНИРУЕМЫХ РЕЗУЛЬТАТОВ ОБУЧЕНИЯ ПО ДИСЦИПЛИНЕ

Процесс изучения дисциплины «Интегральные устройства радиоэлектроники» направлен на формирование следующих компетенций:

ОПК-5 — Способен разрабатывать алгоритмы и компьютерные программы, пригодные для практического применения.

| T0          | Результаты обучения, характеризующие                                                                                                                                   |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Компетенция | сформированность компетенции                                                                                                                                           |

| ОПК-5       | знать состав и методику разработки моделей сложно-функциональных блоков с использованием схемного редактора                                                            |

|             | уметь разрабатывать функциональные узлы и сложно-функциональные блоки с использованием библиотек стандартных элементов, моделировать и получать их временные параметры |

|             | владеть навыками отладки и верификации моделей сложно-функциональных блоков, реализовывать прототипы устройств с использованием отладочных плат                        |

#### 4 ОБЪЕМ ДИСЦИПЛИНЫ

Общая трудоемкость дисциплины «Интегральные устройства радиоэлектроники» составляет 5 зачётных единиц.

Распределение трудоемкости дисциплины по видам занятий

| Вид учебной работы                    | Всего | Семестры |

|---------------------------------------|-------|----------|

|                                       | часов | 8        |

| Аудиторные занятия (всего)            | 72    | 72       |

| В том числе:                          |       |          |

| Лекции                                | 24    | 24       |

| Практические занятия (ПЗ)             |       |          |

| Лабораторные работы (ЛР)              | 48    | 48       |

| Самостоятельная работа                | 81    | 81       |

| Курсовой проект                       | +     | +        |

| Контрольная работа                    |       |          |

| Вид промежуточной аттестации –экзамен | 27    | 27       |

| Общая трудоемкость час                | 180   | 180      |

| зач. ед.                              | 5     | 5        |

Заочная форма обучения

| Вид учебной работы                     | Всего | Семестры |

|----------------------------------------|-------|----------|

|                                        | часов | 10       |

| Аудиторные занятия (всего)             | 12    | 12       |

| В том числе:                           |       |          |

| Лекции                                 | 4     | 4        |

| Практические занятия (ПЗ)              |       |          |

| Лабораторные работы (ЛР)               | 8     | 8        |

| Самостоятельная работа                 | 159   | 159      |

| Курсовой проект                        | +     | +        |

| Контрольная работа                     |       |          |

| Вид промежуточной аттестации – экзамен | 9     | 9        |

| Общая трудоемкость час                 | 180   | 180      |

| зач. ед.                               | 5     | 5        |

# 5 СОДЕРЖАНИЕ ДИСЦИПЛИНЫ

# 5.1 Содержание разделов дисциплины и распределение трудоемкости по видам занятий

Очная форма обучения

|                 | o man popula ody remin                                                                               |                                                                                                                                                                                                    |      |              |     |            |  |

|-----------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----|------------|--|

| <b>№</b><br>п/п | Наименование темы                                                                                    | Содержание раздела                                                                                                                                                                                 | Лекц | Лаб.<br>зан. | CPC | Всего, час |  |

| 1               | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования | <ol> <li>Принципы построения и функционирования<br/>шифраторов и дешифраторов.</li> <li>Принципы построения и функционирования<br/>мультиплексоров. Реализация демультиплек-<br/>соров.</li> </ol> | 8    | 16           | 27  | 51         |  |

Заочная форма обучения

| №<br>п/п | Наименование темы                                                                                          | Содержание раздела                                                                                                                                                                                                                                                                                                                                                                                                    | Лекц | Лаб.<br>зан. | CPC | Всего, час |

|----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----|------------|

| 1        | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования       | <ol> <li>Принципы построения и функционирования шифраторов и дешифраторов.</li> <li>Принципы построения и функционирования мультиплексоров. Реализация демультиплексоров.</li> <li>Общие сведения об арифметических цифровых узлах. Полусумматоры. Полные сумматоры. Цифровые компараторы.</li> <li>Преобразователи кодов, классификация двоичных кодов и их синтез.</li> </ol>                                       | 2    | 4            | 53  | 59         |

| 2        | Проектирование цифровых функциональных узлов последовательностного типа на вентильном уровне моделирования | 1. Триггер как элемент памяти: структурная схема триггера, роль составляющих частей триггера, назначение входов триггера. Асинхронный и синхронный триггеры. Асинхронный RS — триггер, одноступенчатый синхронный RS — триггер, D — тригтер со статическим и динамическим входами, JK-триггер: схема, таблица истинности, переключательная функция, функционирование. Преобразование JK — триггера в RS — , D — , Т — | 2    | 2            | 53  | 57         |

| Реализация и верификация мо-<br>делей цифровых функциональ-<br>ных узлов с использованием<br>отладочных плат ПЛИС | триггеры.  2. Регистры хранения, сдвигающие, реверсивные. Регистровые делители частоты и генераторы псевдослучайных последовательностей.  3. Принципы построения и функционирования суммирующих, вычитающих и реверсивных счетчиков. Способы обеспечения заданного модуля счета.  4. Цифровые автоматы  1. Программируемые логические матрицы (ПЛМ), программируемая матричная логика (ПМЛ). Базовые матричные кристаллы (БМК). Программируемые структуры СРLD и FPGA.  2. Программируемые логические интегральные схемы (ПЛИС) типа FPGA. Общие сведения. Архитектура и основные модули программируемых логических интегральных схем типа FPGA. Логические блоки, система коммутации, блоки ввода/вывода.  3. Использование схем с программируемой структурой (ПЛИС). Маршрут проектирования цифровых устройств на ПЛИС. Про- |   | 2 | 53  | 55  |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----|-----|

|                                                                                                                   | 3. Использование схем с программируемой структурой (ПЛИС). Маршрут проектирования цифровых устройств на ПЛИС. Программируемые логические интегральные схемы Xilinx семейства Spartan 3E.  4. Структура «Система на кристалле» и «Система в копусе»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |   |     |     |

|                                                                                                                   | Итого                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 | 8 | 159 | 171 |

Практическая подготовка при освоении дисциплины учебным планом не предусмотрена.

#### 5.2 Перечень лабораторных работ

- 1. Проектирование и верификация шифраторов и дешифраторов в системе автоматизированного проектирования.

- 2. Проектирование и верификация мультиплексоров и демультиплексоров в системе автоматизированного проектирования.

- 3. Проектирование и верификация сумматоров и цифровых компараторов в системе автоматизированного проектирования.

- 4. Проектирование и верификация преобразователей кодов в системе автоматизированного проектирования.

- 5. Проектирование и верификация триггеров RS, JK, D, T типа в системе автоматизированного проектирования

- 6. Проектирование и верификация регистров в системе автоматизированного проектирования

- 7. Проектирование и верификация счетчиков в системе автоматизированного проектирования

- 8. Проектирование и верификация цифровых автоматов в системе автоматизированного проектирования

- 9. Физическая верификация цифровых устройств с использованием отладочных плат ПЛИС

- 10. Разработка программного интерфейса клавиатуры отладочной платы ПЛИС

### 6 ПРИМЕРНАЯ ТЕМАТИКА КУРСОВЫХ ПРОЕКТОВ (РАБОТ) И КОНТРОЛЬНЫХ РАБОТ

В соответствии с учебным планом освоение дисциплины предусматривает выполнение курсового проекта в 8 семестре для очной формы обучения и на 5 курсе для заочной формы обучения.

Примерная тематика курсового проекта: «Проектирование оперативного запоминающего устройства статического типа»

Задачи, решаемые при выполнении курсового проекта:

- Разработка схемы запоминающего устройства.

- Верификация полученной модели, построение временных диаграмм.

- Физическая верификация модели с использованием отладочной платы ПЛИС

Курсовой проект включает в себя графическую часть и расчетно-пояснительную записку.

# 7 ОЦЕНОЧНЫЕ МАТЕРИАЛЫ ДЛЯ ПРОВЕДЕНИЯ ПРОМЕЖУТОЧНОЙ АТТЕСТАЦИИ ОБУЧАЮЩИХСЯ ПО ДИСЦИПЛИНЕ

# 7.1 Описание показателей и критериев оценивания компетенций на различных этапах их формирования, описание шкал оценивания

#### 7.1.1 Этап текущего контроля

Результаты текущего контроля знаний и межсессионной аттестации оцениваются по следующей системе:

«аттестован»;

«не аттестован».

| Компе-<br>тенция | Результаты обучения, характеризующие<br>сформированность компетенции | Критерии<br>оценивания | Аттестован       | Не аттестован |

|------------------|----------------------------------------------------------------------|------------------------|------------------|---------------|

| ОПК-5            | знать состав и методику разработки мо-                               | Отвечает на теоре-     | Выполнение ра-   | Невыполнение  |

|                  | делей сложно-функциональных блоков с                                 | тические вопросы       | бот в срок, пре- | работ в срок, |

|                  | использованием схемного редактора                                    | при устном опросе      | дусмотренный в   | предусмотрен- |

|                  |                                                                      | и защите лабора-       | рабочих про-     | ный в рабочих |

|                  |                                                                      | торной работы.         | граммах          | программах    |

|                  | уметь разрабатывать функциональные                                   | Активно работает       | Выполнение ра-   | Невыполнение  |

|                  | узлы и сложно-функциональные блоки с                                 | на лабораторных        | бот в срок, пре- | работ в срок, |

|                  | использованием библиотек стандартных                                 | занятиях.              | дусмотренный в   | предусмотрен- |

|                  | элементов, моделировать и получать их                                |                        | рабочих про-     | ный в рабочих |

|                  | временные параметры                                                  |                        | граммах          | программах    |

|                  | владеть навыками отладки и верифика-                                 | Высокий уровень        | Выполнение ра-   | Невыполнение  |

|                  | ции моделей сложно-функциональных                                    | самостоятельности      | бот в срок, пре- | работ в срок, |

|                  | блоков, реализовывать прототипы уст-                                 | при выполнении         | дусмотренный в   | предусмотрен- |

|                  | ройств с использованием отладочных                                   | лабораторных работ     | рабочих про-     | ный в рабочих |

|                  | плат                                                                 | и оформлении от-       | граммах          | программах    |

|                  |                                                                      | четов                  |                  |               |

#### 7.1.2 Этап промежуточного контроля знаний

Результаты промежуточного контроля знаний оцениваются в 8 семестре для очной формы обучения и в 10 семестре для заочной формы обучения по системе:

«отлично»; «хорошо»; «удовлетворительно»; «неудовлетворительно».

| Комп<br>е-<br>тенци<br>я | Результаты обучения, характеризующие<br>сформированность компетенции                                                                            | Критерии<br>оценивани<br>я    | Отлично                                                                  | Хорошо                                                                                 | Удовл.                                                                         | Неудовл.                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|

| ОПК-<br>5                | знать состав и методику разработки моделей сложно-функциональных блоков с использованием схемного редактора                                     |                               | Выполнен<br>ие теста на<br>90- 100%                                      | Выполнени<br>е теста на<br>80- 90%                                                     | Выполнение<br>теста на 70-<br>80%                                              | В тесте менее 70% правильных ответов |

|                          | но-функциональные блоки с ис-                                                                                                                   | стандартны<br>х<br>практическ | Задачи<br>решены в<br>полном<br>объеме и<br>получены<br>верные<br>ответы | Продемонстр ирован верный ход решения всех, но не получен верный ответ во всех задачах | Проде-<br>монстр иро-<br>ван верный<br>ход решения<br>в большин-<br>стве задач | Задачи не решены                     |

|                          | владеть навыками отладки и верификации моделей сложно-функциональных блоков, реализовывать прототипы устройств с использованием отладочных плат | прикладных<br>задач в         | Задачи<br>решены в<br>полном<br>объеме и<br>получены<br>верные<br>ответы | Продемонстр ирован верный ход решения всех, но не получен верный ответ во всех задачах | Проде-<br>монстр иро-<br>ван верный<br>ход решения<br>в большин-<br>стве задач | Задачи не решены                     |

7.2 Примерный перечень оценочных средств (типовые контрольные задания или иные материалы, необходимые для оценки знаний, умений, навыков и (или) опыта деятельности)

### 7.2.1 Примерный перечень заданий для подготовки к тестированию

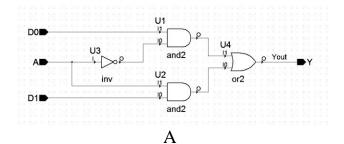

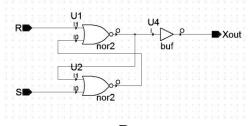

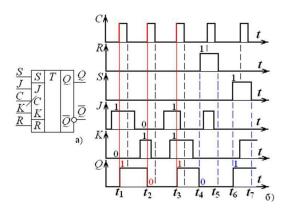

1. Выберете рисунок, на котором изображен RS-триггер

2. Установите взаимно-однозначное соответствие между этапами проектирования модели на логическом уровне и необходимым программным инструментом.

Схемный редактор система автоматизированного проектирования Xilinx ISE и его функциональное назначение инструментов. Заполните таблицу.

| 1. | Компоновка элементов и блоков схемы на черте-   | A | ISim              |

|----|-------------------------------------------------|---|-------------------|

|    | же                                              |   |                   |

| 2. | Трассировка в соответствии со структурой схемой | В | Add Wire          |

| 3. | Назначение портов ввода\вывода                  | С | Design/Simulation |

| 4. | Программное моделирование, симуляция            | D | Add I\O Marker    |

| 5. | Визуализация и анализ результатов               | Е | Add Symbol        |

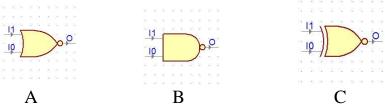

3. Какой из указанных элементов следует исключить, как не соответствующий базисам «2ИЛИ-НЕ» и «2И-НЕ»?

- 4. Расположите операции получения временных диаграмм в верном порядке

- А Назначение симуляторов входных сигналов;

- В Добавление портов ввода\вывода в поле симулятора;

- С Регистрация выходных характеристик;

- D Установка времени симуляции.

- 5. В качестве средств описания выступают модели различных уровней сложности. Какие модели используются для проектирования цифровых устройств?

- А. Логическая модель;

- В. Регрессионная модель;

- С. Модель с временными задержками;

- D. Модель с учетом электрических эффектов (или электрическая модель).

- 6. Какой символ в начале строки согласно синтаксису запрещает обращение к элементу (строке назначения порта ввода\вывода) файла конфигурации Basys.ucf?

$$A - \langle\langle 0 \rangle\rangle$$

,  $B - \langle\langle 1 \rangle\rangle$ ,  $C - \langle\langle 4 \rangle\rangle$ ,  $D - \langle\langle 0 \rangle\rangle$

7. Заполнить таблицу истинности JK – триггера с асинхронными RS входами.

Таблица истинности является важным инструментом описания работы цифровых устройств, одним из элементов маршрута построения моделей на логическом уровне, показывается связь между логическим выражением, логической схемой и временной диаграммой

Работа ЈК-триггера описывается характеристическим уравнением.

$$Q^{t+1} = \overline{Q^t} J + Q^t \overline{K}$$

Временные диаграммы приведены на рисунке ниже.

Условно-графическое обозначение (a) и временная диаграмма (б) работы ЈК-триггера с асинхронными RS входами

|   | Таблица истинно | сти ЈК-триггера | Бланк зад |

|---|-----------------|-----------------|-----------|

| J | K               | $Q_t$           | $Q_{t+1}$ |

| X |                 |                 |           |

|   |                 |                 |           |

|   |                 |                 |           |

|   | X               |                 |           |

|                                                   | Проверяемый критерий |                  |           |           |  |

|---------------------------------------------------|----------------------|------------------|-----------|-----------|--|

| 3aı                                               | полненная таблица и  | стинности ЈК-трі | иггера    |           |  |

| J                                                 | K                    | Qt               | $Q_{t+1}$ |           |  |

| X                                                 | 0                    | 0                | 0         |           |  |

| 0                                                 | 1                    | 0                | 1         | 0 / 1 / 2 |  |

| 1                                                 | 0                    | 1                | 0         |           |  |

| 0                                                 | X                    | 1                | 1         |           |  |

| 0 – в таблице до 1 – в таблице до 2 – таблица зап |                      |                  |           |           |  |

8. В качестве элементов трассировки модулей логической схемы могут быть использованы как одноразрядные проводники, так и шины данных. По-

яснить порядок и особенности применения данного программного инструмента трассировки.

Ключ для проверки правильного ответа.

| Проверяемый критерий                                                  | Балл |

|-----------------------------------------------------------------------|------|

| Шины размещаются на схеме, в отличии от проводников проходят между    | 2    |

| многоразрядными портами функциональных узлов. Шине необходимо         |      |

| задавать в свойствах имя и разрядность. К шине нельзя подключать про- |      |

| водники, не являющиеся компонентами шины, которым присваиваться       |      |

| индекс в зависимости от разряда, к которому они относятся. Левая гра- |      |

| ница диапазона индексов, задающих ширину шины, всегда соответствует   |      |

| старшему значению разряда.                                            |      |

| Шины размещаются на схеме, в отличие от проводников проходят между    | 1    |

| многоразрядными портами функциональных узлов. Шине необходимо         | _    |

| задавать в свойствах имя и разрядность.                               |      |

| Не соответствует ни одному из заданных требований                     |      |

|                                                                       | 0    |

9. Пояснить работу симуляторов, с помощью которых можно устанавливать постоянный длительный уровень (верхний или нижний) сигнала информационной последовательности при моделировании.

Ключ для проверки правильного ответа.

| Проверяемый критерий                                                   | Балл |

|------------------------------------------------------------------------|------|

| Длительное временное воздействие можно задавать по средствам стиму-    | 2    |

| ляторов Formula (задание входных сигналов по указанной закономерно-    |      |

| сти), Value (задание фиксированного значения сигнала на весь временной |      |

| диапазон моделирования), Hotkey (переключение состояний входных        |      |

| сигналов с использованием «горячих клавиш» клавиатуры). Симулятор      |      |

| Clock для данного случая не подходит, ввиду программных ограничений    |      |

| на длительность импульса и паузы.                                      |      |

| Длительное временное воздействие можно задавать по средствам стиму-    | 1    |

| ляторов Value (задание фиксированного значения сигнала на весь вре-    |      |

| менной диапазон моделирования), Hotkey (переключение состояний         |      |

| входных сигналов с использованием «горячих клавиш» клавиатуры).        |      |

| Не соответствует ни одному из заданных требований                      | 0    |

10. Модель цифрового функционального узла получена, проведено тестирование, получены временные диаграммы. Для проведения физической верификации проекта необходимо провести работу с отладочной платой. Перечислите операции необходимые для непосредственного программирования отладочной платы Digilent Basys 2.

Ключ для проверки правильного ответа.

| Tune 1 Aun inpersonal inputation of the fun.                       |      |

|--------------------------------------------------------------------|------|

| Проверяемый критерий                                               | Балл |

| Выбрать режим работы отладочной платы. Поставить перемычку в режим | 2    |

| «РС», для программирования микросхемы FPGA XC3S250E или в режим    |      |

| «ROM» для установки прошивки в энергонезависимую память PROM.      |      |

| Подключить отладочную плату к ПК, удаление предыдущей прошивки     |      |

| выполнять необязательно, система при подтверждении произведет по- |   |

|-------------------------------------------------------------------|---|

| следовательно стирание и программирование интегральной схемы.     |   |

| Перед программированием необходимо подключить отладочную плату к  | 1 |

| ПК, осуществить удаление предыдущей прошивки и произвести про-    |   |

| граммирование.                                                    |   |

| Не соответствует ни одному из заданных требований                 | 0 |

# 7.2.2 Примерный перечень заданий для решения стандартных задач

Получить минимизированную ДНФ с помощью карты Карно (диаграммы Вейча), построить схему на логических элементах, построить временную диаграмму

- 1)  $f = abcd \lor abc \lor abd \lor acd \lor abcd \lor bcd \lor abcd;$

- 2)  $f = \overline{abc} \lor \overline{acd} \lor bc\overline{d} \lor abcd \lor acd \lor \overline{abcd} \lor \overline{abcd};$

- 3)  $f = abcd \lor acd \lor acd \lor abd \lor abcd \lor abcd \lor adc;$

- 4)  $f = \overline{abcd} \lor \overline{abc} \lor \overline{acd} \lor \overline{abcd} \lor \overline{abc} \lor \overline{acd} \lor \overline{abcd};$

- 5)  $f = \overline{acd} \lor \overline{acd} \lor bcd \lor abc\overline{d} \lor \overline{abcd} \lor abc\overline{d} \lor \overline{bcd};$

- 6)  $f = a\overline{bcd} \lor \overline{abcd} \lor \overline{abcd} \lor abd \lor \overline{abc} \lor ac\overline{d} \lor \overline{acd};$

- 7)  $f = \overline{acd} \lor \overline{abd} \lor \overline{acd} \lor \overline{abcd} \lor \overline{abcd} \lor \overline{abcd} \lor \overline{abcd}$

- 8)  $f = \overline{abc} \lor \overline{abcd} \lor \overline{abc} \lor abc \lor abc \overline{d} \lor \overline{abc} \overline{d} \lor \overline{acd} \lor abc \overline{d} \lor acd;$

- 9)  $f = \overline{acd} \lor \overline{abcd} \lor \overline{acd} \lor \overline{abd} \lor \overline{abcd} \lor a\overline{bd};$

- 10)  $f = abcd \lor \overline{abc} \lor \overline{bcd} \lor bcd \lor abd \lor \overline{abcd} \lor \overline{abcd};$

#### 7.2.3 Примерный перечень заданий для решения прикладных задач

По булевой функции, заданной таблицей истинности, построить схемы в базисе «ЗИ-НЕ» и «ИЛИ-НЕ», построить временную диаграмму, провести отладку и физическую верификацию модели

#### Таблица

| $X_1X_2X_3$ | $f^{'}$ | $f^{^{2}}$ | $f^{^3}$ | $f^4$ | $f^{5}$ | $f^{^6}$ | $f^7$ | $f^{^8}$ |

|-------------|---------|------------|----------|-------|---------|----------|-------|----------|

| 0 0 0       | 0       | 1          | 0        | 0     | 0       | 1        | 0     | 1        |

| 0 0 1       | 0       | 0          | 1        | 0     | 1       | 0        | 0     | 0        |

| 0 1 0       | 0       | 0          | 0        | 1     | 1       | 0        | 1     | 1        |

| 0 1 1       | 0       | 0          | 0        | 1     | 0       | 0        | 0     | 0        |

| 1 0 0       | 1       | 0          | 0        | 0     | 0       | 1        | 1     | 1        |

| 1 0 1       | 0       | 0          | 0        | 0     | 0       | 1        | 0     | 0        |

| 1 1 0       | 1       | 0          | 1        | 1     | 1       | 0        | 1     | 1        |

| 1 1 1       | 1       | 0          | 0        | 1     | 1       | 0        | 0     | 0        |

# 7.2.4 Примерный перечень вопросов для подготовки к зачету

Не предусмотрено учебным планом

#### 7.2.5 Примерный перечень вопросов для подготовки к экзамену

- 1. Д триггер типа «защелка»: схема, таблица истинности,  $\Pi\Phi$ , функционирование.

- 2. Преобразование JK триггера в RS , Д , Т триггеры.

- 3. Функциональные узлы цифровых устройств.

- 4. Принципы построения и функционирования одноступенчатых де-

шифраторов.

- 5. Полусумматор: схема, функционирование.

- 6. Полный комбинационный одноразрядный сумматор: схема, функционирование.

- 7. Схема сравнения.

- 8. Принципы построения и функционирования мультиплексоров.

- 9. Принципы построения и функционирования демультиплексоров.

- 10. Реализация шифраторов.

- 11. Регистр хранения: схемы, функционирование.

- 12. Сдвигающие регистры: схемы, функционирование.

- 13. Реверсивный регистр: схема, функционирование.

- 14. Арифметический эквивалент сдвига двоичного кода.

- 15. Регистровые делители частоты: схема, функционирование.

# 7.2.6 Методика выставления оценки при проведении промежуточной аттестации

Экзамен проводится по тест-билетам, каждый из которых содержит 10 вопросов и задачу. Каждый правильный ответ на вопрос в тесте оценивается 1 баллом, задача оценивается в 10 баллов (5 баллов верное решение и 5 баллов за верный ответ). Максимальное количество набранных баллов — 20.

- 1. Оценка «Неудовлетворительно» ставится в случае, если студент набрал менее 6 баллов.

- 2. Оценка «Удовлетворительно» ставится в случае, если студент набрал от 6 до 10 баллов

- 3. Оценка «Хорошо» ставится в случае, если студент набрал от 11 до 15 баллов.

- 4. Оценка «Отлично» ставится, если студент набрал от 16 до 20 баллов.

7.2.7 Паспорт оценочных материалов

| <b>№</b><br>п/п | Контролируемые разделы (темы)<br>дисциплины                                                                | Код контролируемо й компетенции | Наименование<br>оценочного средства                                                           |

|-----------------|------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------|

| 1               | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования       |                                 | Тест, вопросы к защите лабораторных работ, требования к курсовому проекту, вопросы к экзамену |

| 2               | Проектирование цифровых функциональных узлов последовательностного типа на вентильном уровне моделирования |                                 | Тест, вопросы к защите лабораторных работ, требования к курсовому проекту, вопросы к экзамену |

| 3               | Реализация и верификация моделей цифровых функциональных узлов с использованием отладочных плат ПЛИС       | ОПК-5                           | Тест, вопросы к защите лабораторных работ, требования к курсовому проекту, вопросы к экзамену |

# 7.3 Методические материалы, определяющие процедуры оценивания знаний, умений, навыков и (или) опыта деятельности

Тестирование осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных тест-заданий на бумажном носителе. Время тестирования 30 мин. Затем осуществляется проверка теста экзаменатором и выставляется оценка согласно методике выставления оценки при проведении промежуточной аттестации.

Решение стандартных задач осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных задач на бумажном носителе. Время решения задач 30 мин. Затем осуществляется проверка решения задач экзаменатором и выставляется оценка, согласно методике выставления оценки при проведении промежуточной аттестации.

Решение прикладных задач осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных задач на бумажном носителе. Время решения задач 30 мин. Затем осуществляется проверка решения задач экзаменатором и выставляется оценка, согласно методике выставления оценки при проведении промежуточной аттестации.

Защита курсового проекта или отчета по всем видам практик осуществляется согласно требованиям, предъявляемым к работе, описанным в методических материалах. Примерное время защиты на одного студента составляет 20 мин.

### 8 УЧЕБНО МЕТОДИЧЕСКОЕ И ИНФОРМАЦИОННОЕ ОБЕСПЕЧЕНИЕ ДИСЦИПЛИНЫ

### 8.1 Перечень учебной литературы, необходимой для освоения дисциплины

- 1. Кретов С.Д. Интегральные устройства радиоэлектроники : учеб. пособие. Воронеж : ВГТУ, 2004. 146 с.

- 2. Пирогов А. А. Проектирование интегральных схем и их функциональных узлов: учеб. пособие / А. А. Пирогов. Воронеж: Издательство Воронежского государственного университета, 2014. 85 с.

- 3. Пирогов, А. А. Проектирование цифровых функциональных узлов на основе программируемых логических интегральных схем [Электронный ресурс]: практикум / ФГБОУ ВО "Воронеж. гос. техн. ун-т", каф. конструирования и производства радиоаппаратуры. Воронеж: Воронежский государственный технический университет, 2018. 93 с.: ил.: табл. Библиогр.: с.77 (4 назв.). ISBN 978-5-7731-0649-4.— Режим доступа: Пирогов А.А. Проектирование цифровых функциональных узлов на основе программируемых логических интегральных схем.

- 4. Тарасов И. Е. Программируемые логические схемы и их применение в схемотехнических решениях: учеб. пособие / И.Е. Тарасов, Е.Ф. Певцов. М.: ФГБОУ ВПО «Московский государственный технический университет радиотехники, электроники и автоматики», 2012. 184 с.

- 5. Сигачева, В. В. Проектирование автоматизированных систем управления. Проектирование электронных устройств в системе P-CAD : учебное пособие / В. В. Сигачева. Санкт-Петербург : Санкт-Петербургский государственный университет промышленных технологий и дизайна, 2017. 123 с. ISBN 978-5-7937-1367-2. Текст : электронный // Электронно-библиотечная система IPR BOOKS : [сайт]. URL: <a href="https://www.iprbookshop.ru/102665.html">https://www.iprbookshop.ru/102665.html</a>

- 6. Строгонов А.В. Проектирование цифровых устройств в базисе ПЛИС: лабораторный практикум: учеб. пособие [Электронный ресурс]. Электрон. текстовые и граф. данные (3,7 Мб) / А.В. Строгонов, Н.Н. Кошелева, А.Б. Буслаев. Воронеж: ФГБОУ ВО «Воронежский государственный технический университет», 2017. Режим доступа: Строгонов А.В. Проектирование цифровых устройств в базисе ПЛИС

- 7. Методические указания по самостоятельной работе по дисциплине «Интегральные устройства радиоэлектроники» направление 211000.62 «Конструирование и технология электронных средств» (профиль «Проектирование радиоэлектронных И технология средств») всех форм обучения [Электронный ресурс] / Каф. конструирования и производства радиоаппаратуры, Сост.: А. В. Турецкий, Н. В. Ципина, А. А. Пирогов. - Электрон. текстовые, граф. дан. (281 Кб). - Воронеж : ФГБОУ ВПО «Воронежский государственный технический университет», 2015. – Режим доступа: SRS IUR.

- 8.2 Перечень информационных технологий, используемых при осуществлении образовательного процесса по дисциплине, включая перечень лицензионного программного обеспечения, ресурсов информационно-телекоммуникационной сети «Интернет», современных профессиональных баз данных и информационных справочных систем:

Перечень  $\Pi O$ , включая перечень лицензионного программного обеспечения:

OC Windows 7 Pro;

Google Chrome;

Microsoft Office 64-bit;

Компас 3D:

Altium Designer;

DesignSpark PCB

Ресурсы информационно-телекоммуникационной сети «Интернет»:

http://window.edu.ru – единое окно доступа к информационным ресурсам;

http://www.edu.ru/ – федеральный портал «Российское образование»;

Образовательный портал ВГТУ;

$\underline{http://www.iprbookshop.ru/} - \mathtt{электронная}\ \mathsf{библиотечная}\ \mathsf{система}$  IPRbooks;

www.elibrary.ru - научная электронная библиотека

Профессиональные базы данных, информационные справочные системы:

## 9 МАТЕРИАЛЬНО-ТЕХНИЧЕСКАЯ БАЗА, НЕОБХОДИМАЯ ДЛЯ ОСУЩЕСТВЛЕНИЯ ОБРАЗОВАТЕЛЬНОГО ПРОЦЕССА

Учебная аудитория для проведения лекционных занятий, оснащенная следующим оборудованием:

- персональный компьютер с установленным ПО, подключенный к сети Интернет;

- доска магнитно-маркерная;

- мультимедийный проектор на кронштейне;

- экран настенный

Учебная аудитория (лаборатория) для проведения лабораторных занятий, оснащенная следующим оборудованием:

- персональные компьютеры с установленным ПО, эмуляторами KP580 и EMURK286, подключенные к сети Интернет 14 шт.;

- источник питания HY3020E- 9350 6 шт.;

- источник питания Б5-49 3 шт.;

- осциллограф GDS 5 шт.;

- осциллограф цифровой запоминающий ОЦ3С02;

- универсальный генератор сигналов DG1022 4 шт.;

- цифровой осциллограф MSO2072A;

- электронная программируемая нагрузка AEL-8320 4 шт.;

- вольтметр В7-16A;

- частотомер MS6100;

- частотомер Ч3-35A

Помещение (Читальный зал) для самостоятельной работы с выходом в сеть «Интернет» и доступом в электронно-библиотечные системы и электронно-информационную среду, укомплектованное следующим оборудованием:

- персональные компьютеры с установленным ПО, подключенные к сети Интернет  $10~{\rm mr.}$ ;

- принтер;

- магнитно-маркерная доска;

- переносные колонки;

- переносной микрофон.

### 10 МЕТОДИЧЕСКИЕ УКАЗАНИЯ ДЛЯ ОБУЧАЮЩИХСЯ ПО ОСВОЕНИЮ ДИСЦИПЛИНЫ

По дисциплине «Интегральные устройства радиоэлектроники» читаются лекции, проводятся лабораторные работы, выполняется курсовой проект.

Основой изучения дисциплины являются лекции, на которых излагаются наиболее существенные и трудные вопросы, а также вопросы, не нашедшие отражения в учебной литературе. Лекции представляет собой систематическое, последовательное изложение учебного материала. Это — одна из важнейших форм учебного процесса и один из основных методов преподавания в вузе. На лекциях от студента требуется не просто внимание, но и самостоятельное оформление конспекта. Качественный конспект должен легко восприниматься зрительно, в его тексте следует соблюдать абзацы, выделять заголовки, нумеровать формулы, подчеркивать термины. В качестве ценного совета рекомендуется записывать не каждое слово лектора (иначе можно потерять мысль и начать писать автоматически, не вникая в смысл), а постараться понять основную мысль лектора, а затем записать, используя понятные сокращения.

Лабораторные работы выполняются на лабораторном оборудовании в соответствии с методиками, приведенными в указаниях к выполнению работ.

Самостоятельная работа студентов способствует глубокому усвоению учебного материала и развитию навыков самообразования. Самостоятельная работа предполагает ряд составляющих (см. таблицу ниже). Кроме базовых учебников рекомендуется самостоятельно использовать имеющиеся в библиотеке учебно-методические пособия. Независимо от вида учебника, работа с ним должна происходить в течение всего семестра. Эффективнее работать с учебником не после, а перед лекцией. При ознакомлении с каким-либо разделом рекомендуется прочитать его целиком, стараясь уловить общую логику изложения темы. При повторном чтении хорошо акцентировать внимание на ключевых вопросах и основных теоремах (формулах). Можно составить их краткий конспект.

Степень усвоения материала проверяется следующими видами контроля:

- текущий (опрос, контрольные работы, типовые расчеты);

- рубежный (коллоквиум);

- промежуточный (курсовая работа или курсовой проект, зачет, зачет с оценкой, экзамен).

Формами промежуточной аттестации для дисциплины «Интегральные устройства радиоэлектроники» являются экзамен и курсовой проект.

| Вид учебных занятий | Деятельность студента                                       |

|---------------------|-------------------------------------------------------------|

| Лекция              | Написание конспекта лекций: кратко, схематично, последова-  |

|                     | тельно фиксировать основные положения, выводы, формули-     |

|                     | ровки, обобщения; помечать важные мысли, выделять клю-      |

|                     | чевые слова, термины. Проверка терминов, понятий с помо-    |

|                     | щью энциклопедий, словарей, справочников с выписыванием     |

|                     | толкований в тетрадь. Обозначение вопросов, терминов, ма-   |

|                     | териала, которые вызывают трудности, поиск ответов в реко-  |

|                     | мендуемой литературе. Если самостоятельно не удается разо-  |

|                     | браться в материале, необходимо сформулировать вопрос и     |

|                     | задать преподавателю на лекции или на практическом занятии. |

| Лабораторная работа | Лабораторные работы позволяют научиться применять теоре-    |

|                     | тические знания, полученные на лекции при решении кон-      |

|                     | кретных задач. Чтобы наиболее рационально и полно исполь-   |

|                           | _                                                          |

|---------------------------|------------------------------------------------------------|

|                           | зовать все возможности лабораторных для подготовки к ним   |

|                           | необходимо: следует разобрать лекцию по соответствующей    |

|                           | теме, ознакомится с соответствующим разделом учебника,     |

|                           | проработать дополнительную литературу и источники, решить  |

|                           | задачи и выполнить другие письменные задания.              |

| Самостоятельная работа    | Самостоятельная работа студентов способствует глубокому    |

|                           | усвоению учебного материала и развитию навыков самообра-   |

|                           | зования. Самостоятельная работа предполагает следующие     |

|                           | составляющие:                                              |

|                           | - работа с текстами: учебниками, справочниками, дополни-   |

|                           | тельной литературой, а также проработка конспектов лекций; |

|                           | - выполнение домашних заданий и расчетов;                  |

|                           | - работа над темами для самостоятельного изучения;         |

|                           | - участие в работе студенческих научных конференций,       |

|                           | олимпиад;                                                  |

|                           | - подготовка к промежуточной аттестации.                   |

| Курсовой проект           | Методика выполнения курсового проекта изложена в учеб-     |

|                           | но-методическом пособии. Выполнять этапы курсового про-    |

|                           | екта студент должен своевременно и в установленные сроки.  |

|                           | Контроль усвоения материала дисциплины производится про-   |

|                           | веркой курсового проекта, защитой курсового проекта.       |

| Подготовка к промежуточ-  | Готовиться к промежуточной аттестации следует системати-   |

| ной аттестации (экзамену) | чески, в течение всего семестра. Интенсивная подготовка    |

|                           | должна начаться не позднее, чем за месяц-полтора до проме- |

|                           | жуточной аттестации. Данные перед экзаменом три дня эф-    |

|                           | фективнее всего использовать для повторения и систематиза- |

|                           | ции материала.                                             |

|                           |                                                            |