**МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ

РОССИЙСКОЙ ФЕДЕРАЦИИ**

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«Воронежский государственный технический университет»

УТВЕРЖДАЮ

Небольсин В.А.

«29» июня 2018 г.

**РАБОЧАЯ ПРОГРАММА**

дисциплины

**«Специализированные БИС и устройства функциональной

электроники в приборостроении»**

**Направление подготовки 12.03.01 Приборостроение**

**Профиль Приборостроение**

**Квалификация выпускника бакалавр**

**Нормативный период обучения 4 года / 4 года и 11 м.**

**Форма обучения очная / заочная**

**Год начала подготовки 2018**

Автор программы

/Пирогов А.А./

Заведующий кафедрой

Конструирования и

производства

радиоаппаратуры

/Муратов А.В./

Руководитель ОПОП

/Муратов А.В./

Воронеж 2018

## **1. ЦЕЛИ И ЗАДАЧИ ДИСЦИПЛИНЫ**

### **1.1. Цели дисциплины**

изучение базовых понятий в области цифровой схемотехники и обработки сигналов, подготовка квалифицированного проектировщика, обладающего достаточным объемом знаний в области цифровой схемотехники, умеющего разрабатывать цифровые устройства с использованием языков описания аппаратуры.

### **1.2. Задачи освоения дисциплины**

1. обучение основным понятиям, моделям и параметрам логических элементов

2. получение представления об основах цифровой обработки сигнала и их области применения

3. получение знаний в области проектирования и работы основных типов функциональных узлов цифровой схемотехники получение навыков в области проектирования цифровых устройств с использованием современных программных комплексов

## **2. МЕСТО ДИСЦИПЛИНЫ В СТРУКТУРЕ ОПОП**

Дисциплина «Специализированные БИС и устройства функциональной электроники в приборостроении» относится к дисциплинам части, формируемой участниками образовательных отношений блока Б1.

## **3. ПЕРЕЧЕНЬ ПЛАНИРУЕМЫХ РЕЗУЛЬТАТОВ ОБУЧЕНИЯ ПО ДИСЦИПЛИНЕ**

Процесс изучения дисциплины «Специализированные БИС и устройства функциональной электроники в приборостроении» направлен на формирование следующих компетенций:

ПК-2 - Способен выполнять математическое моделирование физических процессов с использованием стандартных пакетов автоматизированного проектирования согласно техническому заданию

| <b>Компетенция</b> | <b>Результаты обучения, характеризующие сформированность компетенции</b>                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ПК-2               | <p>Знать состав и методику разработки моделей цифровых функциональных узлов с использованием схемного редактора</p> <p>Уметь разрабатывать цифровые функциональные узлы с использованием библиотек стандартных элементов, моделировать и получать их временные параметры</p> <p>Владеть навыками отладки и верификации моделей цифровых функциональных узлов, реализовывать прототипы устройств с использованием отладочных плат</p> |

## 4. ОБЪЕМ ДИСЦИПЛИНЫ

Общая трудоемкость дисциплины «Специализированные БИС и устройства функциональной электроники в приборостроении» составляет 4 з.е.

### Распределение трудоемкости дисциплины по видам занятий **очная форма обучения**

| Виды учебной работы                             | Всего часов | Семестры |  |

|-------------------------------------------------|-------------|----------|--|

|                                                 |             | 7        |  |

| <b>Аудиторные занятия (всего)</b>               | 72          | 72       |  |

| В том числе:                                    |             |          |  |

| Лекции                                          | 36          | 36       |  |

| Лабораторные работы (ЛР)                        | 36          | 36       |  |

| <b>Самостоятельная работа</b>                   | 72          | 72       |  |

| Виды промежуточной аттестации - зачет с оценкой | +           | +        |  |

| Общая трудоемкость:<br>академические часы       | 144         | 144      |  |

| зач.ед.                                         | 4           | 4        |  |

### **заочная форма обучения**

| Виды учебной работы                             | Всего часов | Семестры |  |

|-------------------------------------------------|-------------|----------|--|

|                                                 |             | 9        |  |

| <b>Аудиторные занятия (всего)</b>               | 20          | 20       |  |

| В том числе:                                    |             |          |  |

| Лекции                                          | 8           | 8        |  |

| Лабораторные работы (ЛР)                        | 14          | 14       |  |

| <b>Самостоятельная работа</b>                   | 118         | 118      |  |

| Часы на контроль                                | 4           | 4        |  |

| Виды промежуточной аттестации - зачет с оценкой | +           | +        |  |

| Общая трудоемкость:<br>академические часы       | 144         | 144      |  |

| зач.ед.                                         | 4           | 4        |  |

## 5. СОДЕРЖАНИЕ ДИСЦИПЛИНЫ (МОДУЛЯ)

### **5.1 Содержание разделов дисциплины и распределение трудоемкости по видам занятий**

#### **очная форма обучения**

| № п/п | Наименование темы                                                                                    | Содержание раздела                                                                                                                                                                                                                                                                                                                 | Лекц | Лаб. зан. | СРС | Всего, час |

|-------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-----|------------|

| 1     | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования | 1. Принципы построения и функционирования шифраторов и дешифраторов.<br>2. Принципы построения и функционирования мультиплексоров. Реализация демультиплексоров.<br>3. Общие сведения об арифметических цифровых узлах. Полусумматоры. Полные сумматоры. Цифровые компараторы.<br>4. Преобразователи кодов, классификация двоичных | 12   | 12        | 24  | 48         |

|              |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |           |           |            |

|--------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|------------|

|              |                                                                                                            | кодов и их синтез.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |           |           |            |

| 2            | Проектирование цифровых функциональных узлов последовательностного типа на вентильном уровне моделирования | <p>1. Триггер как элемент памяти: структурная схема триггера, роль составляющих частей триггера, назначение входов триггера. Асинхронный и синхронный триггеры. Асинхронный RS – триггер, одноступенчатый синхронный RS – триггер, D – триггер со статическим и динамическим входами, JK-триггер: схема, таблица истинности, переключательная функция, функционирование. Преобразование JK – триггера в RS – , D – , T – триггеры.</p> <p>2. Регистры хранения, сдвигающие, реверсивные. Регистровые делители частоты и генераторы псевдослучайных последовательностей.</p> <p>3. Принципы построения и функционирования суммирующих, вычитающих и реверсивных счетчиков. Способы обеспечения заданного модуля счета.</p> <p>4. Цифровые автоматы</p> | 12        | 12        | 24        | 48         |

| 3            | Реализация и верификация моделей цифровых функциональных узлов с использованием отладочных плат ПЛИС       | <p>1. Программируемые логические матрицы (ПЛМ), программируемая матричная логика (ПМЛ). Базовые матричные кристаллы (БМК). Программируемые структуры CPLD и FPGA.</p> <p>2. Программируемые логические интегральные схемы (ПЛИС) типа FPGA. Общие сведения. Архитектура и основные модули программируемых логических интегральных схем типа FPGA. Логические блоки, система коммутации, блоки ввода/вывода.</p> <p>3. Использование схем с программируемой структурой (ПЛИС). Маршрут проектирования цифровых устройств на ПЛИС. Программируемые логические интегральные схемы Xilinx семейства Spartan 3E.</p> <p>4. Структура «Система на кристалле» и «Система в копусе»</p>                                                                       | 12        | 12        | 24        | 48         |

| <b>Итого</b> |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>36</b> | <b>36</b> | <b>72</b> | <b>144</b> |

### **заочная форма обучения**

| №<br>п/п | Наименование темы                                                                                          | Содержание раздела                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Лекц | Лаб.<br>зан. | СРС | Всего,<br>час |

|----------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----|---------------|

| 1        | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования       | <p>1. Принципы построения и функционирования шифраторов и дешифраторов.</p> <p>2. Принципы построения и функционирования мультиплексоров. Реализация демультиплексоров.</p> <p>3. Общие сведения об арифметических цифровых узлах. Полусумматоры. Полные сумматоры. Цифровые компараторы.</p> <p>4. Преобразователи кодов, классификация двоичных кодов и их синтез.</p>                                                                                                                                                                                                                                                                                                                                                                              | 2    | 4            | 40  | 46            |

| 2        | Проектирование цифровых функциональных узлов последовательностного типа на вентильном уровне моделирования | <p>1. Триггер как элемент памяти: структурная схема триггера, роль составляющих частей триггера, назначение входов триггера. Асинхронный и синхронный триггеры. Асинхронный RS – триггер, одноступенчатый синхронный RS – триггер, D – триггер со статическим и динамическим входами, JK-триггер: схема, таблица истинности, переключательная функция, функционирование. Преобразование JK – триггера в RS – , D – , T – триггеры.</p> <p>2. Регистры хранения, сдвигающие, реверсивные. Регистровые делители частоты и генераторы псевдослучайных последовательностей.</p> <p>3. Принципы построения и функционирования суммирующих, вычитающих и реверсивных счетчиков. Способы обеспечения заданного модуля счета.</p> <p>4. Цифровые автоматы</p> | 2    | 4            | 40  | 46            |

| 3        | Реализация и верификация моделей                                                                           | 1. Программируемые логические матрицы (ПЛМ), программируемая матричная логика (ПМЛ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4    | 6            | 38  | 48            |

|  |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |   |    |     |     |

|--|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|----|-----|-----|

|  | цифровых функциональных узлов с использованием отладочных плат ПЛИС | Базовые матричные кристаллы (БМК). Программируемые структуры CPLD и FPGA.<br>2. Программируемые логические интегральные схемы (ПЛИС) типа FPGA. Общие сведения. Архитектура и основные модули программируемых логических интегральных схем типа FPGA. Логические блоки, система коммутации, блоки ввода/вывода.<br>3. Использование схем с программируемой структурой (ПЛИС). Маршрут проектирования цифровых устройств на ПЛИС. Программируемые логические интегральные схемы Xilinx семейства Spartan 3E.<br>4. Структура «Система на кристалле» и «Система в копусе» |       |   |    |     |     |

|  |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Итого | 8 | 14 | 120 | 140 |

## 5.2 Перечень лабораторных работ

Укажите перечень лабораторных работ

1. Проектирование и верификация шифраторов и дешифраторов в системе автоматизированного проектирования.

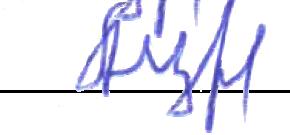

2. Проектирование и верификация мультиплексоров и демультиплексоров в системе автоматизированного проектирования.

3. Проектирование и верификация сумматоров и цифровых компараторов в системе автоматизированного проектирования.

4. Проектирование и верификация преобразователей кодов в системе автоматизированного проектирования.

5. Проектирование и верификация триггеров RS, JK, D, T - типа в системе автоматизированного проектирования

6. Проектирование и верификация регистров в системе автоматизированного проектирования

7. Проектирование и верификация счетчиков в системе автоматизированного проектирования

8. Проектирование и верификация цифровых автоматов в системе автоматизированного проектирования

9. Физическая верификация цифровых устройств с использованием отладочных плат ПЛИС

10. Разработка программного интерфейса клавиатуры отладочной платы ПЛИС

## 6. ПРИМЕРНАЯ ТЕМАТИКА КУРСОВЫХ ПРОЕКТОВ (РАБОТ) И КОНТРОЛЬНЫХ РАБОТ

В соответствии с учебным планом освоение дисциплины не предусматривает выполнение курсового проекта (работы) или контрольной работы.

## 7. ОЦЕНОЧНЫЕ МАТЕРИАЛЫ ДЛЯ ПРОВЕДЕНИЯ ПРОМЕЖУТОЧНОЙ АТТЕСТАЦИИ ОБУЧАЮЩИХСЯ ПО ДИСЦИПЛИНЕ

**7.1. Описание показателей и критериев оценивания компетенций на различных этапах их формирования, описание шкал оценивания**

### 7.1.1 Этап текущего контроля

Результаты текущего контроля знаний и межсессионной аттестации оцениваются по следующей системе:

«аттестован»;

«не аттестован».

| Компетенция | Результаты обучения, характеризующие сформированность компетенции                                                                                 | Критерии оценивания                                                                                          | Аттестован                                                    | Не аттестован                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|

| ПК-2        | Знать состав и методику разработки моделей цифровых функциональных узлов с использованием схемного редактора                                      | Активная работа на практических занятиях, ответ не менее чем на половину заданных в процессе опроса вопросов | Выполнение работ в срок, предусмотренный в рабочих программах | Невыполнение работ в срок, предусмотренный в рабочих программах |

|             | Уметь разрабатывать цифровые функциональные узлы с использованием библиотек стандартных элементов, моделировать и получать их временные параметры | Решение не менее половины стандартных практических задач                                                     | Выполнение работ в срок, предусмотренный в рабочих программах | Невыполнение работ в срок, предусмотренный в рабочих программах |

|             | Владеть навыками отладки и верификации моделей цифровых функциональных узлов, реализовывать прототипы устройств с использованием отладочных плат  | Решение не менее половины прикладных задач в конкретной предметной области                                   | Выполнение работ в срок, предусмотренный в рабочих программах | Невыполнение работ в срок, предусмотренный в рабочих программах |

### 7.1.2 Этап промежуточного контроля знаний

Результаты промежуточного контроля знаний оцениваются в 7 семестре для очной формы обучения, 9 семестре для заочной формы обучения по четырехбалльной системе:

«отлично»;

«хорошо»;

«удовлетворительно»;

«неудовлетворительно».

| Компетенция | Результаты обучения, характеризующие сформированность компетенции | Критерии оценивания | Отлично                     | Хорошо                     | Удовл.                     | Неудовл.                             |

|-------------|-------------------------------------------------------------------|---------------------|-----------------------------|----------------------------|----------------------------|--------------------------------------|

| ПК-2        | Знать состав и методику разработки моделей                        | Тест                | Выполнение теста на 90-100% | Выполнение теста на 80-90% | Выполнение теста на 70-80% | В тесте менее 70% правильных ответов |

|                                                                                                                                                   |                                                          |                                                        |                                                                                       |                                                          |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|

| цифровых функциональных узлов с использованием схемного редактора                                                                                 |                                                          |                                                        |                                                                                       |                                                          |                  |

| Уметь разрабатывать цифровые функциональные узлы с использованием библиотек стандартных элементов, моделировать и получать их временные параметры | Решение стандартных практических задач                   | Задачи решены в полном объеме и получены верные ответы | Продемонстрирован верный ход решения всех, но не получен верный ответ во всех задачах | Продемонстрирован верный ход решения в большинстве задач | Задачи не решены |

| Владеть навыками отладки и верификации моделей цифровых функциональных узлов, реализовывать прототипы устройств с использованием отладочных плат  | Решение прикладных задач в конкретной предметной области | Задачи решены в полном объеме и получены верные ответы | Продемонстрирован верный ход решения всех, но не получен верный ответ во всех задачах | Продемонстрирован верный ход решения в большинстве задач | Задачи не решены |

## 7.2 Примерный перечень оценочных средств (типовые контрольные задания или иные материалы, необходимые для оценки знаний, умений, навыков и (или) опыта деятельности)

### 7.2.1 Примерный перечень заданий для подготовки к тестированию

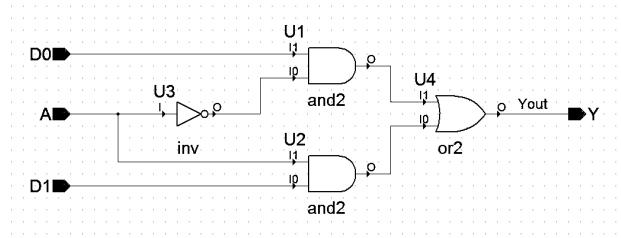

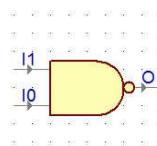

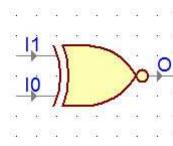

1. Выберете рисунок, на котором изображен RS-триггер

A

B

Ответ: В

**2.** Установите взаимно-однозначное соответствие между этапами проектирования модели на логическом уровне и необходимым программным инструментом.

Схемный редактор системы автоматизированного проектирования Xilinx ISE и его функциональное назначение инструментов. Заполните таблицу.

|    |                                                 |   |                   |

|----|-------------------------------------------------|---|-------------------|

| 1. | Компоновка элементов и блоков схемы на чертеже  | A | ISim              |

| 2. | Трассировка в соответствии со структурой схемой | B | Add Wire          |

| 3. | Назначение портов ввода\вывода                  | C | Design/Simulation |

| 4. | Программное моделирование, симуляция            | D | Add I/O Marker    |

| 5. | Визуализация и анализ результатов               | E | Add Symbol        |

Ответ:

|   |   |   |   |   |

|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 |

| E | B | D | C | A |

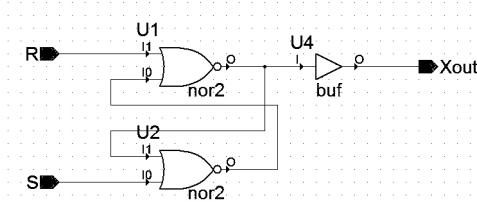

**3.** Какой из указанных элементов следует исключить, как не соответствующий базисам «2ИЛИ-НЕ» и «2И-НЕ»?

A

B

C

Ответ: C

**4.** Расположите операции получения временных диаграмм в верном порядке

- A – Назначение симуляторов входных сигналов;

- B – Добавление портов ввода\вывода в поле симулятора;

- C – Регистрация выходных характеристик;

- D – Установка времени симуляции.

Ответ:

|   |   |   |   |

|---|---|---|---|

| 1 | 2 | 3 | 4 |

| B | A | D | C |

**5.** В качестве средств описания выступают модели различных уровней сложности. Какие модели используются для проектирования цифровых устройств?

- A. Логическая модель;

- B. Регрессионная модель;

- C. Модель с временными задержками;

D. Модель с учетом электрических эффектов (или электрическая модель).

Ответ: A, C, D

6. Какой символ в начале строки согласно синтаксису запрещает обращение к элементу (строке назначения порта ввода\вывода) файла конфигурации Basys.ucf?

A – «%», B – «\$», C – «#», D – «@»

Ответ: C

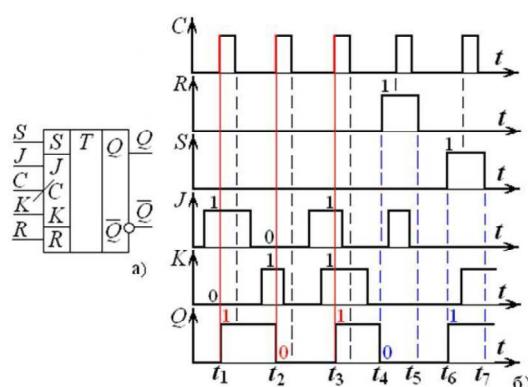

7. Заполнить таблицу истинности JK – триггера с асинхронными RS входами.

Таблица истинности является важным инструментом описания работы цифровых устройств, одним из элементов маршрута построения моделей на логическом уровне, показывается связь между логическим выражением, логической схемой и временной диаграммой

Работа JK-триггера описывается характеристическим уравнением.

$$Q^{t+1} = \overline{Q^t} J + Q^t \bar{K}$$

Временные диаграммы приведены на рисунке ниже.

Условно-графическое обозначение (а) и временная диаграмма (б) работы JK-триггера с асинхронными RS входами

| Бланк задания                  |   |                |                  |

|--------------------------------|---|----------------|------------------|

| Таблица истинности JK-триггера |   |                |                  |

| J                              | K | Q <sub>t</sub> | Q <sub>t+1</sub> |

| X                              |   |                |                  |

|                                |   |                |                  |

|                                |   |                |                  |

|                                | X |                |                  |

Ключ для проверки правильного ответа.

| Проверяемый критерий                       | Балл |

|--------------------------------------------|------|

| Заполненная таблица истинности JK-триггера |      |

| <b>J</b> | <b>K</b> | <b>Q<sub>t</sub></b> | <b>Q<sub>t+1</sub></b> |           |

|----------|----------|----------------------|------------------------|-----------|

| X        | 0        | 0                    | 0                      | 0 / 1 / 2 |

| 0        | 1        | 0                    | 1                      |           |

| 1        | 0        | 1                    | 0                      |           |

| 0        | X        | 1                    | 1                      |           |

0 – в таблице допущены две и более ошибки;

1 – в таблице допущена одна ошибка;

2 – таблица заполнена без ошибок.

**8.** В качестве элементов трассировки модулей логической схемы могут быть использованы как одноразрядные проводники, так и шины данных. Пояснить порядок и особенности применения данного программного инструмента трассировки.

Ключ для проверки правильного ответа.

| <b>Проверяемый критерий</b>                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Балл</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Шины размещаются на схеме, в отличии от проводников проходят между многоразрядными портами функциональных узлов. Шине необходимо задавать в свойствах имя и разрядность. К шине нельзя подключать проводники, не являющиеся компонентами шины, которым присваивается индекс в зависимости от разряда, к которому они относятся. Левая граница диапазона индексов, задающих ширину шины, всегда соответствует старшему значению разряда. | 2           |

| Шины размещаются на схеме, в отличии от проводников проходят между многоразрядными портами функциональных узлов. Шине необходимо задавать в свойствах имя и разрядность.                                                                                                                                                                                                                                                                | 1           |

| Не соответствует ни одному из заданных требований                                                                                                                                                                                                                                                                                                                                                                                       | 0           |

**9.** Пояснить работу симуляторов, с помощью которых можно устанавливать постоянный длительный уровень (верхний или нижний) сигнала информационной последовательности при моделировании.

Ключ для проверки правильного ответа.

| <b>Проверяемый критерий</b>                                                                                                                                                                                                                                                                                                                                                              | <b>Балл</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Длительное временное воздействие можно задавать по средствам стимуляторов Formula (задание входных сигналов по указанной закономерности), Value (задание фиксированного значения сигнала на весь временной диапазон моделирования), Hotkey (переключение состояний входных сигналов с использованием «горячих клавиш» клавиатуры). Симулятор Clock для данного случая не подходит, ввиду | 2           |

|                                                                                                                                                                                                                                                                                                                                                                                   |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| программных ограничений на длительность импульса и паузы. Длительное временное воздействие можно задавать по средствам стимуляторов Value (задание фиксированного значения сигнала на весь временной диапазон моделирования), Hotkey (переключение состояний входных сигналов с использованием «горячих клавиш» клавиатуры).<br>Не соответствует ни одному из заданных требований | 1<br><br>0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

**10.** Модель цифрового функционального узла получена, проведено тестирование, получены временные диаграммы. Для проведения физической верификации проекта необходимо провести работу с отладочной платой. Перечислите операции необходимые для непосредственного программирования отладочной платы Digilent Basys 2.

Ключ для проверки правильного ответа.

| Проверяемый критерий                                                                                                                                                                                                                                                                                                                                                                          | Балл |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Выбрать режим работы отладочной платы. Поставить перемычку в режим «PC», для программирования микросхемы FPGA XC3S250E или в режим «ROM» для установки прошивки в энергонезависимую память PROM. Подключить отладочную плату к ПК, удаление предыдущей прошивки выполнять необязательно, система при подтверждении произведет последовательно стирание и программирование интегральной схемы. | 2    |

| Перед программированием необходимо подключить отладочную плату к ПК, осуществить удаление предыдущей прошивки и произвести программирование.                                                                                                                                                                                                                                                  | 1    |

| Не соответствует ни одному из заданных требований                                                                                                                                                                                                                                                                                                                                             | 0    |

### 7.2.2 Примерный перечень заданий для решения стандартных задач

Получить минимизированную ДНФ с помощью карты Карно (диаграммы Вейча), построить схему на логических элементах, построить временную диаграмму

- 1 )  $f = abcd \vee \overline{abc} \vee \overline{abd} \vee \overline{acd} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{abcd}$ ;

- 2 )  $f = \overline{abc} \vee \overline{acd} \vee \overline{bcd} \vee abcd \vee acd \vee \overline{abcd} \vee \overline{abcd}$ ;

- 3 )  $f = abcd \vee \overline{acd} \vee \overline{acd} \vee \overline{abd} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{ad}c$ ;

- 4 )  $f = \overline{abcd} \vee \overline{abc} \vee \overline{acd} \vee \overline{bcd} \vee \overline{abc} \vee acd \vee \overline{bcd}$ ;

- 5 )  $f = \overline{acd} \vee \overline{acd} \vee \overline{bcd} \vee abcd \vee \overline{bcd} \vee \overline{bcd} \vee \overline{bcd}$ ;

- 6 )  $f = \overline{bcd} \vee \overline{abcd} \vee \overline{bcd} \vee abd \vee \overline{abc} \vee \overline{acd} \vee \overline{acd}$ ;

- 7 )  $f = \overline{acd} \vee \overline{abd} \vee \overline{acd} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{abc}$ ;

- 8 )  $f = \overline{abc} \vee \overline{bcd} \vee \overline{abc} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{acd} \vee \overline{bcd} \vee acd$ ;

- 9 )  $f = \overline{acd} \vee \overline{bcd} \vee \overline{acd} \vee \overline{abd} \vee \overline{bcd} \vee \overline{bcd} \vee \overline{abd}$ ;

- 10 )  $f = abcd \vee \overline{abc} \vee \overline{bcd} \vee bcd \vee abd \vee \overline{bcd} \vee \overline{bcd}$ ;

### **7.2.3 Примерный перечень заданий для решения прикладных задач**

По булевой функции, заданной таблицей истинности построить схемы в базисе «ЗИ-НЕ» и «ИЛИ-НЕ», построить временную диаграмму, провести отладку и физическую верификацию модели

Таблица

| $x_1 x_2 x_3$ | $f^1$ | $f^2$ | $f^3$ | $f^4$ | $f^5$ | $f^6$ | $f^7$ | $f^8$ |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0 0 0         | 0     | 1     | 0     | 0     | 0     | 1     | 0     | 1     |

| 0 0 1         | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 0     |

| 0 1 0         | 0     | 0     | 0     | 1     | 1     | 0     | 1     | 1     |

| 0 1 1         | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1 0 0         | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

| 1 0 1         | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 1 1 0         | 1     | 0     | 1     | 1     | 1     | 0     | 1     | 1     |

| 1 1 1         | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 0     |

### **7.2.4 Примерный перечень вопросов для подготовки к зачету**

Не предусмотрено учебным планом

### **7.2.5 Примерный перечень заданий для решения прикладных задач**

1. Д - триггер типа «защелка»: схема, таблица истинности, ПФ, функционирование.

2. Преобразование JK триггера в RS - , D - , T – триггеры.

3. Функциональные узлы цифровых устройств.

4. Принципы построения и функционирования одноступенчатых дешифраторов.

5. Полусумматор: схема, функционирование.

6. Полный комбинационный одноразрядный сумматор: схема, функционирование.

7. Схема сравнения.

8. Принципы построения и функционирования мультиплексоров.

9. Принципы построения и функционирования демультиплексоров.

10. Реализация шифраторов.

11. Регистр хранения: схемы, функционирование.

12. Сдвигающие регистры: схемы, функционирование.

13. Реверсивный регистр: схема, функционирование.

14. Арифметический эквивалент сдвига двоичного кода.

15. Регистровые делители частоты: схема, функционирование.

### **7.2.6. Методика выставления оценки при проведении промежуточной аттестации**

Зачет с оценкой проводится по тест-билетам, каждый из которых содержит 10 вопросов и задачу. Каждый правильный ответ на вопрос в тесте оценивается 1 баллом, задача оценивается в 10 баллов (5 баллов верное решение и 5 баллов за верный ответ). Максимальное количество набранных баллов – 20.

1. Оценка «Неудовлетворительно» ставится в случае, если студент набрал менее 6 баллов.

2. Оценка «Удовлетворительно» ставится в случае, если студент набрал от 6 до 10 баллов

3. Оценка «Хорошо» ставится в случае, если студент набрал от 11 до 15 баллов.

4. Оценка «Отлично» ставится, если студент набрал от 16 до 20 баллов.

### **7.2.7 Паспорт оценочных материалов**

| № п/п | Контролируемые разделы (темы) дисциплины                                                                   | Код контролируемой компетенции | Наименование оценочного средства |

|-------|------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|

| 1     | Проектирование цифровых функциональных узлов комбинационного типа на вентильном уровне моделирования       | ПК-2                           | Тест, защита лабораторных работ  |

| 2     | Проектирование цифровых функциональных узлов последовательностного типа на вентильном уровне моделирования | ПК-2                           | Тест, защита лабораторных работ  |

| 3     | Реализация и верификация моделей цифровых функциональных узлов с использованием отладочных плат ПЛИС       | ПК-2                           | Тест, защита лабораторных работ  |

### **7.3. Методические материалы, определяющие процедуры оценивания знаний, умений, навыков и (или) опыта деятельности**

Тестирование осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных тест-заданий на бумажном носителе. Время тестирования 30 мин. Затем осуществляется проверка теста экзаменатором и выставляется оценка согласно методики выставления оценки при проведении промежуточной аттестации.

Решение стандартных задач осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных задач на бумажном носителе. Время решения задач 30 мин. Затем осуществляется проверка решения задач экзаменатором и выставляется оценка, согласно методики выставления оценки при проведении промежуточной аттестации.

Решение прикладных задач осуществляется, либо при помощи компьютерной системы тестирования, либо с использованием выданных задач на бумажном носителе. Время решения задач 30 мин. Затем осуществляется проверка решения задач экзаменатором и выставляется оценка, согласно методики выставления оценки при проведении промежуточной аттестации.

## **(8 УЧЕБНО МЕТОДИЧЕСКОЕ И ИНФОРМАЦИОННОЕ ОБЕСПЕЧЕНИЕ ДИСЦИПЛИНЫ)**

### **8.1 Перечень учебной литературы, необходимой для освоения дисциплины**

1. Пирогов А. А. Проектирование интегральных схем и их

функциональных узлов: учеб. пособие / А. А. Пирогов. – Воронеж: Издательство Воронежского государственного университета, 2014. – 85 с.

2. Клочков Г. Л. Цифровые устройства и микропроцессоры: учебник / Г. Л. Клочков. – Воронеж: ВИРЭ, 2005. – 320 с.

3. Угрюмов Е.П. Цифровая схемотехника: учеб. пособие / Е.П. Угрюмов. – СПб.: БХВ-Петербург, 2010. – 810с.

4. Тарасов И. Е. Программируемые логические схемы и их применение в схемотехнических решениях: учеб. пособие / И.Е. Тарасов, Е.Ф. Певцов. – М.: ФГБОУ ВПО «Московский государственный технический университет радиотехники, электроники и автоматики», 2012. – 184с.

**8.2 Перечень информационных технологий, используемых при осуществлении образовательного процесса по дисциплине, включая перечень лицензионного программного обеспечения, ресурсов информационно-телекоммуникационной сети «Интернет», современных профессиональных баз данных и информационных справочных систем:**

1. Xilinx ISE

2. <https://www.xilinx.com/>

3. <https://www.aldec.com/>

4. [kit-e.ru/circuit/изучаем-active-hdl-7-1-урок-1-знакомство с пакетом/](http://kit-e.ru/circuit/izuchаем-active-hdl-7-1-urok-1-znakovstvo-s-paketom/)

## **9 МАТЕРИАЛЬНО-ТЕХНИЧЕСКАЯ БАЗА, НЕОБХОДИМАЯ ДЛЯ ОСУЩЕСТВЛЕНИЯ ОБРАЗОВАТЕЛЬНОГО ПРОЦЕССА**

Учебная аудитория укомплектованное специализированной мебелью, оборудованное техническими средствами обучения: персональными компьютерами с лицензионным программным обеспечением с возможностью подключения к сети «Интернет» и доступом в электронную информационно-образовательную среду университета

## **10. МЕТОДИЧЕСКИЕ УКАЗАНИЯ ДЛЯ ОБУЧАЮЩИХСЯ ПО ОСВОЕНИЮ ДИСЦИПЛИНЫ (МОДУЛЯ)**

По дисциплине «Специализированные БИС и устройства функциональной электроники в приборостроении» читаются лекции, проводятся лабораторные работы.

Основой изучения дисциплины являются лекции, на которых излагаются наиболее существенные и трудные вопросы, а также вопросы, не нашедшие отражения в учебной литературе.

Лабораторные работы выполняются на лабораторном оборудовании в соответствии с методиками, приведенными в указаниях к выполнению работ.

| Вид учебных занятий | Деятельность студента                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Лекция              | Написание конспекта лекций: кратко, схематично, последовательно фиксировать основные положения, выводы, формулировки, обобщения; помечать важные мысли, выделять ключевые слова, термины. Проверка |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | терминов, понятий с помощью энциклопедий, словарей, справочников с выписыванием толкований в тетрадь. Обозначение вопросов, терминов, материала, которые вызывают трудности, поиск ответов в рекомендуемой литературе. Если самостоятельно не удается разобраться в материале, необходимо сформулировать вопрос и задать преподавателю на лекции или на практическом занятии.                                                                                                                                                                                                                       |

| Лабораторная работа                   | Лабораторные работы позволяют научиться применять теоретические знания, полученные на лекции при решении конкретных задач. Чтобы наиболее рационально и полно использовать все возможности лабораторных для подготовки к ним необходимо: следует разобрать лекцию по соответствующей теме, ознакомится с соответствующим разделом учебника, проработать дополнительную литературу и источники, решить задачи и выполнить другие письменные задания.                                                                                                                                                 |

| Самостоятельная работа                | Самостоятельная работа студентов способствует глубокому усвоения учебного материала и развитию навыков самообразования. Самостоятельная работа предполагает следующие составляющие:<br><ul style="list-style-type: none"> <li>- работа с текстами: учебниками, справочниками, дополнительной литературой, а также проработка конспектов лекций;</li> <li>- выполнение домашних заданий и расчетов;</li> <li>- работа над темами для самостоятельного изучения;</li> <li>- участие в работе студенческих научных конференций, олимпиад;</li> <li>- подготовка к промежуточной аттестации.</li> </ul> |

| Подготовка к промежуточной аттестации | Готовиться к промежуточной аттестации следует систематически, в течение всего семестра. Интенсивная подготовка должна начаться не позднее, чем за месяц-полтора до промежуточной аттестации. Данные перед зачетом с оценкой, зачетом с оценкой три дня эффективнее всего использовать для повторения и систематизации материала.                                                                                                                                                                                                                                                                    |