#### А. В. СТРОГОНОВ

## ЦИФРОВАЯ ОБРАБОТКА СИГНАЛОВ В БАЗИСЕ ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ

Учебное пособие

Издание четвертое, стереотипное

УДК 004.383 ББК 32.973я73

С 86 Строгонов А. В. Цифровая обработка сигналов в базисе программируемых логических интегральных схем: учебное пособие для вузов / А. В. Строгонов. — 4-е изд., стер. — Санкт-Петербург: Лань, 2022. — 312 с.: ил. — Текст: непосредственный.

#### ISBN 978-5-8114-9782-9

В учебном пособии рассматривается проектирование устройств цифровой обработки сигналов для реализации в базисе ПЛИС. Даются практические примеры проектирования цифровых фильтров с использованием высокоуровневого языка описания аппаратурных средств VHDL и мегафункций в САПР ПЛИС Altera Quartus II и Xilinx ISE Design Suite.

Издание соответствует требованиям Федерального государственного образовательного стандарта высшего профессионального образования по направлению «Электроника и наноэлектроника» (программа магистерской подготовки «Приборы и устройства в микро- и наноэлектронике»), дисциплинам «Цифровая обработка сигналов», «Архитектуры микропроцессорных вычислительных систем», «САПР БИС программируемой логики», «САПР системного уровня проектирования БИС».

УДК 004.383 ББК 32.973я73

#### Издается в авторской редакции

#### Рецензенты:

В. Б. СТЕШЕНКО — кандидат технических наук, доцент, зам. генерального конструктора ОАО «Российские космические системы»; М. И. ГОРЛОВ — доктор технических наук, профессор Воронежского государственного технического университета.

<sup>©</sup> Издательство «Лань», 2022

<sup>©</sup> А. В. Строгонов, 2022

<sup>©</sup> Издательство «Лань», художественное оформление, 2022

#### **ВВЕДЕНИЕ**

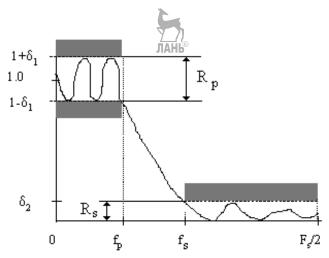

ПЛИС – цифровые БИС высокой степени интеграции, программируемую пользователем внутреннюю имеющие предназначенные для реализации сложных структуру цифровых устройств. Использование ПЛИС и САПР позволяет в сжатые сроки создавать конкурентоспособные устройства и требованиям удовлетворяющие системы, жестким производительности, энергопотреблению, надежности, массогабаритным параметрам, стоимости. Обработка сигналов может осуществляться с помощью различных технических средств. В последнее десятилетие лидирующее положение занимает цифровая обработка сигналов (ЦОС), которая по сравнению с аналоговой имеет следующие преимущества: малую чувствительность к параметрам окружающей среды, простоту перепрограммирования и переносимость алгоритмов. Олной распространённых операций ЦОС является ИЗ фильтрация. Вид импульсной характеристики цифрового фильтра (ЦФ) определяет их деление на ЦФ с конечной импульсной характеристикой (КИХ-фильтры) бесконечной импульсной характеристикой (БИХ-фильтры).

применение цифровых КИХ-фильтров Широкое свойства ИХ исследованы. тем, хорошо вызвано ЧТО Использование особенностей архитектуры ПЛИС позволяет компактные и быстрые КИХ-фильтры проектировать использованием так называемой распределённой арифметики.

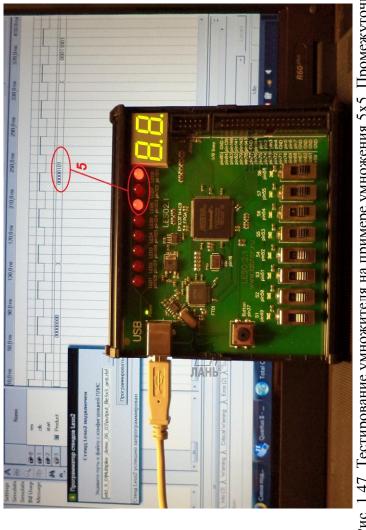

В первой главе рассматриваются основы двоичной арифметики и представление чисел со знаком, основное внимание уделено проектированию умножителей чисел со знаком, представленных в дополнительном коде. Приводятся сведения по программным умножителям в базисе ПЛИС. Дается практический пример по использованию учебного лабораторного стенда LESO2. По (Лаборатории электронных средств обучения, ЛЭСО ГОУ ВПО «СибГУТИ») для отладки

проекта умножителя целых положительных чисел, представленных в прямом коде размерностью 4х4 методом правого сдвига и сложения в базисе ПЛИС серии Cyclone.

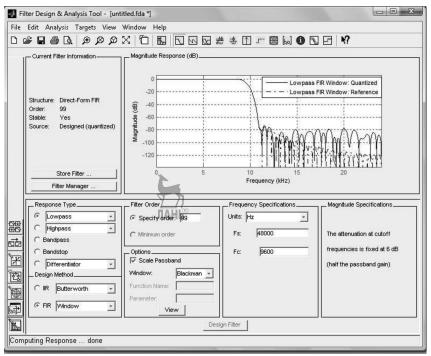

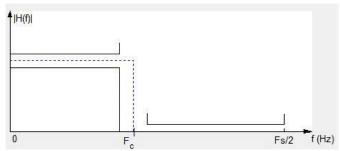

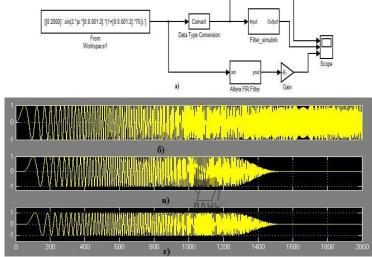

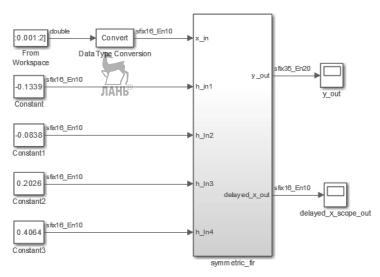

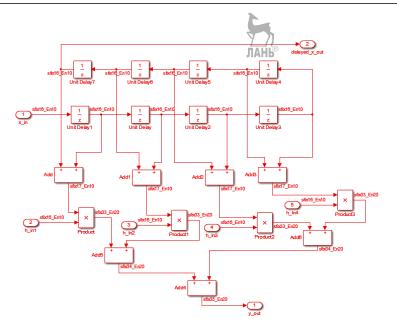

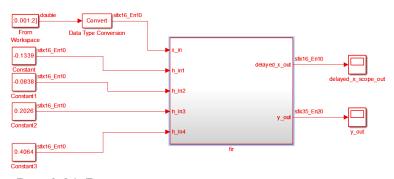

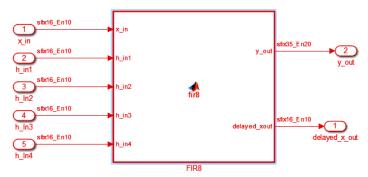

Во второй главе рассматривается моделирование КИХфильтра в системе Matlab/Simulink (пакет Signal Processing, Демонстрируются различные FDATool). реализации параллельных КИХ-фильтров с использованием перемножителей на мегафункциях САПР Quartus II компании Обсуждаются вопросы проектирования Altera. возникающих эффектов квантования при переходе имитационной модели КИХ-фильтра, разработанной в системе Matlab/Simulink к функциональной реализованной в САПР ПЛИС Quartus II компании Altera.

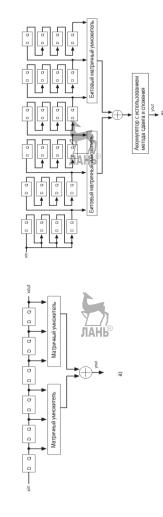

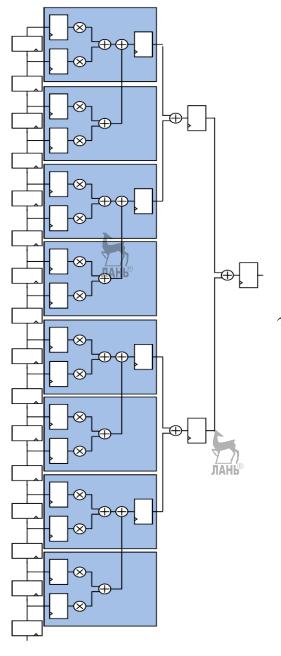

В главе 3 затрагиваются вопросы проектирования высокопроизводительных КИХ-фильтров на последовательной и параллельной распределенных арифметиках, учитывающих архитектурные особенности ПЛИС.

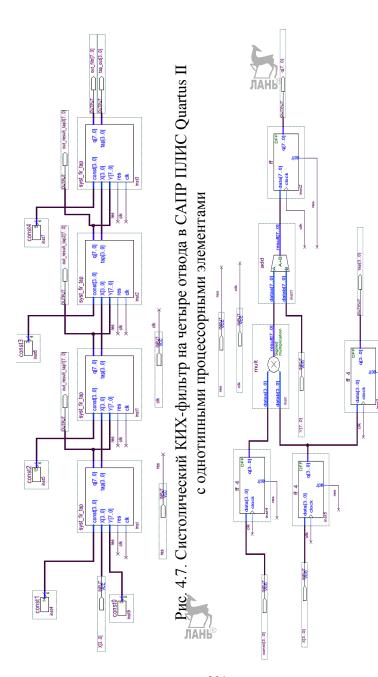

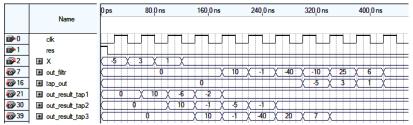

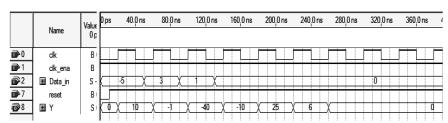

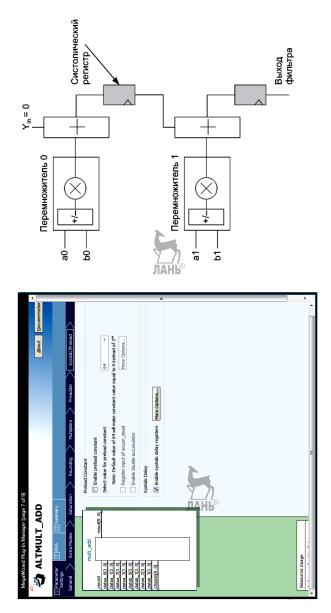

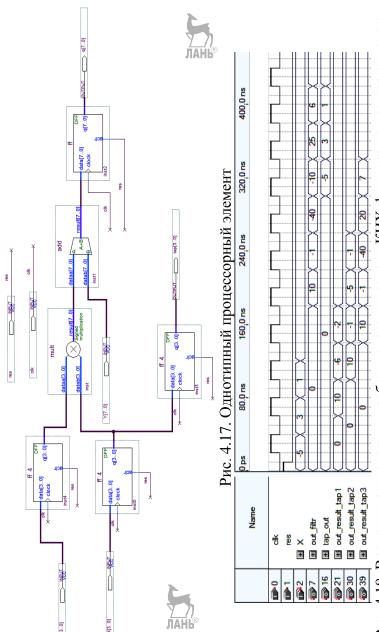

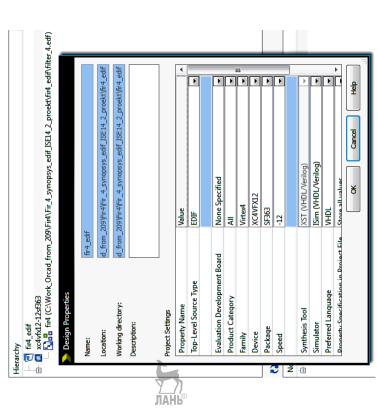

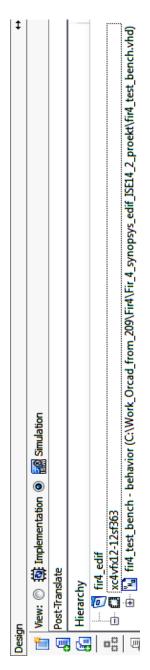

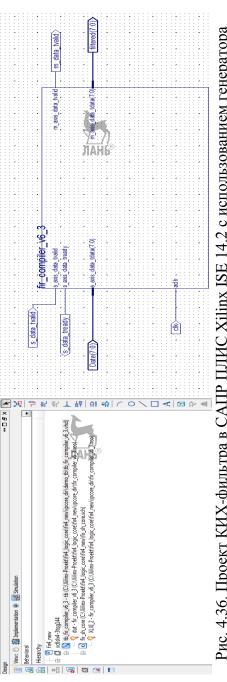

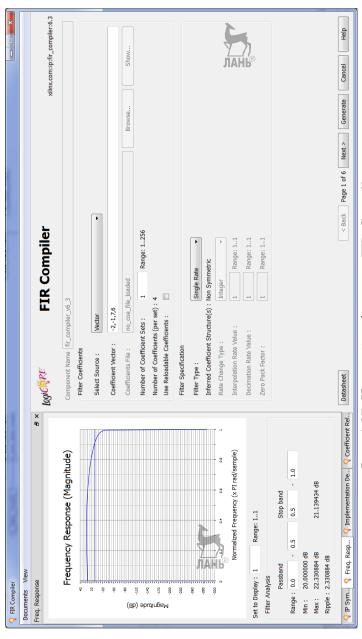

В главе 4 рассматривается проектирование систолических КИХ-фильтров в базисе ПЛИС с использованием системы цифрового моделирования ModelSim-Altera. А также показано использование программы синтеза логики Synplicity совместно с САПР ISE 14.2 для проектирования фильтров в базисе ПЛИС фирмы Xilinx.

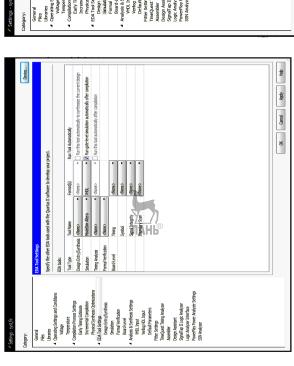

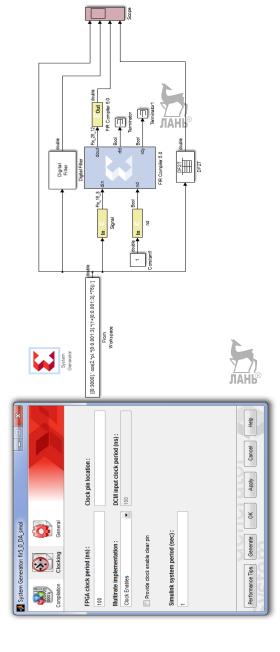

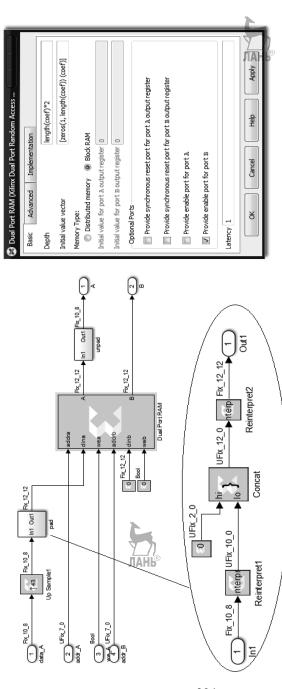

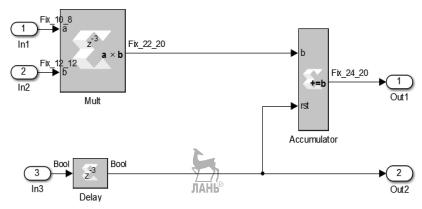

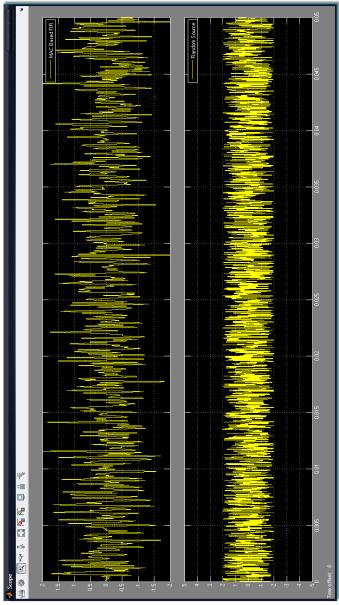

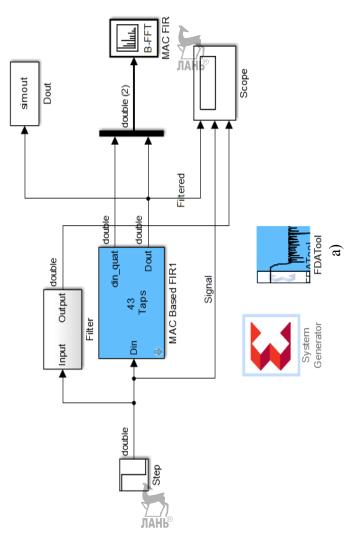

Улелено внимание метолологии ориентированного проектирования с использованием System Generator IDS 14.4 — инструмента для разработки и отладки высокопроизводительных цифровой обработки систем сигналов в базисе ПЛИС фирмы Xilinx в системе визуальномоделирования Matlab/Simulink имитационного 8.0.0.783 (R2012b)). Программный обеспечивает пакет высокоуровневое представление проекта, абстрагированное от конкретной аппаратной платформы, которое автоматически компилируется в ПЛИС Xilinx.

### 1. ПРОЕКТИРОВАНИЕ УМНОЖИТЕЛЕЙ В БАЗИСЕ ПЛИС

### 1.1. Двоичная арифметика

Положительные двоичные числа можно представить только одним способом, а отрицательные двоичные числа тремя способами. В табл. 1.1 приведены в качестве примера лесятичные знаком эквивалентные числа co И их представления прямом, обратном В И дополнительном двоичном коде.

Прямой код. Знак – старший значащий разряд (СЗР) указывает знак (0 – положительный, 1 - отрицательный). Остальные разряды отражают величину, представляющую положительное число:

#### Знак

Это представление чисел удобно для умножения и деления, но при операциях сложения и вычитания нецелесообразно и поэтому используется редко.

В ЭВМ положительные числа представляются в прямом коде, а отрицательные — в виде дополнений, т.е. путем сдвига по числовой оси исходного числа на некоторую константу. Если z — положительное число, то — z представляется в виде K-z, где K таково, что разрядность положительна. Обратный код отличается от дополнительного только выбором значения K.

Дополнение до единицы (обратный код) – отрицательные числа получаются путем инверсии всех разрядов их положительных эквивалентов. Старший значащий разряд указывает знак (0 – положительный, 1 - отрицательный).

Таблица 1.1 Представление чисел в прямом, обратном и дополнительном четырехразрядном двоичном коде

| дополн | нительном чет     | ырсхразрядном              | двоичном коде          |

|--------|-------------------|----------------------------|------------------------|

| ДЧ со  | Прямой            | Обратный                   | Дополнительный         |

| знаком | код               | код*                       | код**                  |

|        | 7                 | (инверсия                  | (инверсия $ X_{10} $ , |

|        | ЛАНЬ <sup>®</sup> | $\left X_{10} ight $ и 1 в | плюс 1 к МЗР и 1 в     |

|        |                   | знаковый                   | знаковый разряд)       |

|        |                   | разряд)                    |                        |

| +7     | 0111              | 0111                       | 0111                   |

| +6     | 0110              | 0110                       | 0110                   |

| +5     | 0101              | 0101                       | 0101                   |

| +4     | 0100              | 0100                       | 0100                   |

| +3     | 0011              | 0011                       | 0011                   |

| +2     | 0010              | 0010                       | 0010                   |

| +1     | 0001              | 0001                       | 0001                   |

| 0      | 0000              | 0000                       | 0000                   |

|        | 1000              | 1111                       |                        |

| -1     | 1001              | 1110                       | 1111                   |

| -2     | 1010              | 1101                       | 1110                   |

| -3     | 1011              | 1100                       | 1101                   |

| -4     | 1100              | 1011                       | 1100                   |

| -5     | 1101              | 1010                       | 1011                   |

| -6     | 1110              | 1001                       | 1010                   |

| -7     | 1111              | 1000                       | 1001                   |

| -8     | 7-)               | -                          | 1000                   |

<sup>\*</sup> при суммировании чисел циклический перенос к МЗР;

Пусть  $X_{10}$  – десятичное число со знаком, которое необходимо представить в обратном коде. Необходимо найти n-разрядное представление числа  $X_{10}$ , включая знак и часть абсолютной величины, которая считается (n-1)-разрядной. Если  $X_{10} \ge 0$ , то обратный код содержит 0 в старшем, знаковом разряде и обычное двоичное представление  $X_{10}$  в

<sup>\*\*</sup> при суммировании чисел перенос игнорируется

остальных n-1 разрядах. Таким образом, для положительных чисел обратный код совпадает с прямым. Если же  $X_{10} \leq 0$ , то знаковый разряд содержит 1, а остальные разряды содержат двоичное представление числа:

$$2^{n-1}-1-|X_{10}|$$

.

Дополнение до единицы формируется очень просто, однако обладает некоторыми недостатками, среди которых двойное представление нуля (все единицы или нули).

Рассмотрим положительное число +13. Выбрав шестиразрядное представление, включая знак (n = 6), получим обратный код, равный 001101. Под абсолютную величину числа отводим пять разрядов. Рассмотрим отрицательное число  $-13_{10}$ , считая представление шестиразрядным, включая знак. В пятиразрядном представлении  $\left|-13_{10}\right| = 13_{10} = 01101_2$  и  $2^5 - 1_{10} = 31_{10} = 11111_2$  тогда

$$(2^{6-1}-1-13)_{10} = (11111-01101)_2 = 10010_2.$$

Добавив шестой, знаковый, разряд, получим шестиразрядный код для  $-13_{10}$ , равный 110010.

Дополнение до двух (дополнительный код). Его труднее сформировать, чем дополнение до единицы, но использованием данного кода удается упростить операции сложения и вычитания. Дополнение до двух образуется путем инверсии каждого разряда положительного числа и последующего добавления единицы к МЗР:

Если  $X_{10} \ge 0$ , то так же, как для прямого и обратного кодов, имеем 0 в знаковом разряде и обычное двоичное представление числа  $X_{10}$  в остальных n-1 разрядах. Если же

$X_{10} < 0$ , то имеем 1 в знаковом разряде, а в остальных n-1 разрядах двоичный эквивалент числа  $2^{n-1} - \left| X_{10} \right|$

Рассмотрим схему сумматора, основанного на поразрядном процессе. Обозначим два складываемых числа через  $A = a_{n-1}a_{n-2}\dots a_1a_0$  и  $B = b_{n-1}b_{n-2}\dots b_1b_0$ . При сложении двоичных чисел значения цифр в каждом двоичном разряде должны быть сложены между собой с переносом из предыдущего разряда. Если результат при этом превышает 1, то возникает перенос в следующий разряд.

Рассмотрим число  $-13_{10}$ . Представим его в шестиразрядном дополнительном коде. Так как  $\left|-13_{10}\right|=13_{10}=01101_2$  и  $2_{10}^5=32_{10}=100000_2$ , то получим в пятиразрядном представлении

$$2^{n-1} - |X_{10}| = (2^{6-1} - 13)_{10} = (100000 - 01101)_2 = 10011_2$$

.

Добавляя шестой знаковый разряд, получаем дополнительный код числа  $-13_{10}$ , равный 110011. Ноль в дополнительном коде имеет единственное представление.

Сложение положительных чисел происходит непосредственно, перенос В НО разряд знака нужно предотвратить и рассматривать как переполнение. Когда складываются два отрицательных числа или отрицательное число с положительным, то работа сумматора зависит от представления отрицательного способа числа. При представлении последних в дополнительном коде сложение осуществляется просто, но необходим дополнительный знаковый разряд, любой перенос за пределы положения знакового разряда просто игнорируется.

Если используется дополнение до единицы, то перенос из знакового разряда должен использоваться как входной перенос к МЗР.

Рассмотрим такое понятие, как "расширение знака". Рассмотрим десятичное число  $-3_{10}$  в дополнительном, а число  $3_{10}$  - прямом кодах в трехразрядном представлении:

в четырехразрядном представлении:

1101

$$(-2^3 + 2^2 + 2^0)$$

0011  $(2^1 + 2^0)$

Таким образом, добавление единиц для отрицательных чисел в дополнительном коде и нулей для положительных чисел старше знакового разряда (дублирование знакового разряда) не изменяет представление десятичного числа, этим свойством воспользуемся при проектировании накапливающего сумматора.

#### 1.2. Представление чисел со знаком

Числа с фиксированной запятой характеризуются длиной слова в битах, положением двоичной точки (binary point) и могут быть беззнаковыми или знаковыми. Позиция двоичной точки определяет число разрядов в целой и дробной частях машинного слова. Для представления знаковых чисел (отрицательных и положительных) старший разряд двоичного слова отводится под знак числа (sign bit). При представлении

беззнаковых чисел с фиксированной точкой разряд знака отсутствует, становится И ОН значимым Отрицательные числа представляются в дополнительном коде. Данные с фиксированной запятой могут быть следующих типов: целыми (integers); дробными (fractional); обобщёнными (generalize). Обобщённый тип не имеет определить позицию двоичной запятой по умолчанию и требует явного указания её положения. Этот тип данных специфицируют ufix и sfix форматами.

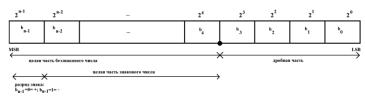

На рис. 1.1 представлено двоичное число с фиксированной запятой обобщенного типа, где  $b_i$  - i-й разряд числа; n - длина двоичного слова в битах;  $b_{n-1}$  - старший значимый разряд (MSB);  $b_0$  - младший значимый разряд (LSB);  $2^i$  - вес i-го разряда числа. Двоичная запятая занимает четвёртую позицию от младшего (LSB) разряда числа. При этом длина дробной части числа m#4.

Рис. 1.1. Формат машинного слова

В файле помощи Fixed-Point Blockset системы Matlab для представления такого числа применяется следующая формула:

V=SQ+B,

где V - точное значение действительного десятичного числа; S - наклон; Q - квантованное (двоично-взвешенное) значение целого числа; B - смещение. Наклон S представляется следующим образом:  $S=Fx2^E$ , где F - наклон дробной части,

нормализованная величина  $1 \le F < 2$ ; E - показатель степени E = -m. При проектировании устройств цифровой обработки сигналов принимают B = 0 и F = 1:

$$V\approx 2^{-m}xQ$$

.

Квантованное значение Q приближённо представляет истинное значение действительного числа V в виде суммы произведений весовых коэффициентов  $b_i$  на веса  $2^i$  соответствующих двоичных разрядов машинного слова; для беззнаковых чисел с фиксированной точкой определяется формулой

$$Q = \sum_{i=0}^{n-1} b_i \times 2^i.$$

Квантованное значение знаковых чисел определяется по формуле

$$Q = -b_{n-1} \times 2^{n-1} + \sum_{i=0}^{n-2} b_i \times 2^i.$$

Так как целые числа не имеют дробной части (m = 0), то выражение для V имеет вид

$$V = \sum_{i=0}^{n} b_i \times 2^i$$

и для знакового целого числа:

$$V = -b_{n-1} \times 2^{n-1} + \sum_{i=0}^{n-2} b_i \times 2^i$$

.

${

m B}$  формате с фиксированной запятой без знака вещественное число V можно считать обозначением полинома

$$V = S * \left[ \sum_{i=0}^{\mathrm{n-l}} b_i 2^i \right].$$

Например, двоичное число в дополнительном коде 0011.0101 при длине машинного слова n=8 и m=4 представляет беззнаковое (MSB = 0) вещественное число 3.3125:

$$3.3125 = 2^{-4} \begin{pmatrix} 0 * 2^7 + 0 * 2^6 + 1 * 2^5 + 1 * 2^4 + 0 * 2^3 + \\ +1 * 2^2 + 0 * 2^1 + 1 * 2^0 \end{pmatrix}.$$

При MSB=1 будем иметь уже другое число -4.6875:  $-4.6875 = 2^{-4} \left( -1*2^7 + 0*2^6 + 1*2^5 + 1*2^4 + 0*2^3 + 1*2^2 + 0*2^1 + 1*2^0 \right).$

### 1.3. Матричные умножители

Существует огромное число разновидностей матричных умножителей, превосходящих ПО скорости последовательностные умножители, основанные на методе сдвига и сложения. Известны и более сложные процедуры, например, с представлением суммирования в древовидном формате. В данном разделе не ставится цель разработать превышающий ПО умножитель, своим техническим характеристикам существующие матричные умножители, а необходимо показать читателю процедуру умножения чисел, представленных в дополнительном коде, методом правого сдвига и сложения, пригодную для реализации в базисе ПЛИС черезвычайно популярную для реализации базисе сигнальных процессоров.

В качестве сравнения рассмотрим один из хорошо известных умножителей чисел в дополнительном коде, так называемый умножитель Бо-Вули (Baugh-Wooley). Если A и B целые десятичные числа со знаком, то в дополнительном двоичном коде представляются в виде:

$$\begin{split} A &= -a_{m-1}2^{m-1} + \sum_{i=0}^{m-2} a_i 2^i \text{ if } X = -x_{n-1}2^{n-1} + \sum_{i=0}^{n-2} x_i 2^i \text{ ,} \\ A &* X = a_{m-1}x_{n-1}2^{m+n-2} + \\ &\text{TO} + \sum_{i=0}^{m-2} \sum_{j=0}^{n-2} a_i x_j 2^{i+j} - \sum_{i=0}^{m-2} x_{n-1} a_i 2^{i+n-1} - \sum_{j=0}^{n-2} a_{m-1} x_j 2^{j+m-1} \text{ .} \end{split}$$

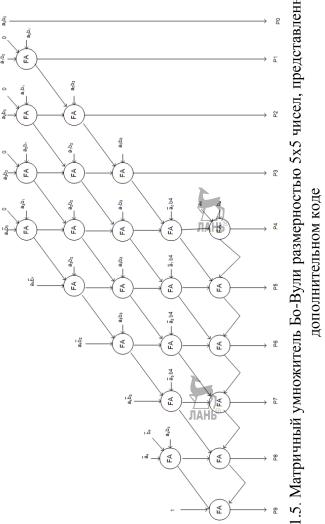

На рис. 1.2 показан пример умножения чисел 5х5, представленных дополнительным кодом по формуле, а на рис. 1.3 - пример умножения чисел 5х5, представленных дополнительным кодом по схеме Бо-Вули. На рис. 1.4 преобразований, позволяющая схема перевести показана частичные произведения со знаком в беззнаковые величины. 1.5 показан матричный умножитель Бо-Вули размерностью 5х5 чисел, представленных в дополнительном коде. Наличие полных сумматоров (FA) в матричной структуре умножителя является главным достоинством для реализации в базисе заказных БИС, a недостатком пониженное быстродействие за счет увеличения столбца с 5 до 7.

Ниже показы примеры умножения для различных случаев по схеме Бо-Вули (рис. 1.6).

Рис. 1.2. Пример умножения чисел 5x5, представленных дополнительным кодом по формуле

Рис. 1.3. Пример умножения чисел 5х5, представленных дополнительным кодом по схеме Бо-Вули

$$-a_{4} X_{i} = a_{4} (1-x_{i}) - a_{4} = a_{4} \overline{x_{i}} - a_{4}$$

$$-a_{4} X_{i} = a_{4} (1-x_{i}) - a_{4} = a_{4} \overline{x_{i}} - a_{4}$$

$$-a_{4} A_{5} = a_{4} (1-x_{i}) - a_{4} = a_{4} \overline{x_{i}} - a_{4}$$

$$-a_{4} A_{5} = a_{4} (1-x_{i}) - a_{4} = a_{4} \overline{x_{i}} - a_{4}$$

$$-a_{4} A_{5} = a_{4} (1-x_{i}) - x_{4} = x_{4} \overline{a_{i}} - x_{4}$$

$$-a_{4} A_{5} = a_{4} \overline{x_{i}} - x_{4}$$

$$-a_{4} A_{5} = a_{4} \overline{x_{i}} - a_{4}$$

$$-a_{4} A_{5} = a_{4} \overline{x_{i}} - a_$$

Рис. 1.4. Схема преобразований Бо-Вули

Рис. 1.5. Матричный умножитель Бо-Вули размерностью 5х5 чисел, представленных в

# Случай 1.

Множимое - положительное число Множитель - отрицательное число

| =13          | = -5         |   |              |   |              |   |   |   | = -65 |

|--------------|--------------|---|--------------|---|--------------|---|---|---|-------|

| ~            | _            | - |              |   |              |   |   |   | ~     |

| 0            | -            | 0 | <del>-</del> |   |              |   |   |   | -     |

| <del>-</del> | 0            | - | 0            | 0 |              |   |   |   | -     |

| <del>-</del> | <del>-</del> | ~ | ~            | 0 | <del>v</del> |   |   |   | -     |

| 0            | ~            | 0 | ~            | 0 | 0            | 0 | 0 | - | ~     |

|              |              |   | 0            | 0 | ~            | ~ |   |   | -     |

|              |              |   |              | 0 | <del></del>  | 0 |   |   | 0     |

|              |              |   |              |   | 0            | 0 |   |   | ~     |

|              | X            |   |              |   | 0            | ~ | 0 |   | ~     |

|              | . `          |   |              |   |              |   |   | + | -     |

# Случай 3.

Множимое и множитель - положительные числа — о 1 1 0 1 = 13

# Случай 2.

Множитель - положительное число Множимое - отрицательное число

| ņ | =13 |    |   |   |               |   |   |              |   | = -65 |

|---|-----|----|---|---|---------------|---|---|--------------|---|-------|

| - | _   | ١, | - |   |               |   |   |              |   | ~     |

| - | 0   | ١, | - | 0 |               |   |   |              |   | ~     |

| 0 | ~   | ١, | ) | 0 | <del></del>   |   |   |              |   | -     |

| - | ~   | ١, | - | 0 | $\overline{}$ | _ |   |              |   | ~     |

| - | 0   | ٠  | 0 | 0 | 0             | ~ | 0 | ~            | 0 | ~     |

|   |     |    |   | ~ | ~             | 0 | 0 |              |   | -     |

|   |     |    |   |   | 0             | ~ | ~ |              |   | 0     |

|   |     |    |   |   |               | 0 | 0 |              |   | ~     |

|   | x   |    |   |   |               | 0 | 0 | <del>-</del> |   | ~     |

|   | ,   |    |   |   |               |   |   |              | + | -     |

# Случай 4.

Множимое и множитель - отрицательные числа

0 0 0

Рис. 1.6. Примеры умножения для различных случаев по схеме Бо-Вули

## 1.4. Проектирование умножителя методом правого сдвига и сложения с управляющим автоматом в базисе ПЛИС

Для проектирования КИХ-фильтров в базисе процессоров цифровой обработки сигналов (ЦОС-процессор) используется общепринятая методика умножения с накоплением с применением так называемых МАС-блоков из-за отсутствия встроенных комбинационных умножителей.

Использование данного метода для умножения чисел в базисе сигнальных процессоров является чрезвычайно популярным у разработчиков РЭА. На базе данного метода реализуются схемы быстрого умножения (например, кодирование по Буту, которое позволяет уменьшать число частичных произведений вдвое, умножение по основанию 4, модифицированное кодирование по Буту).

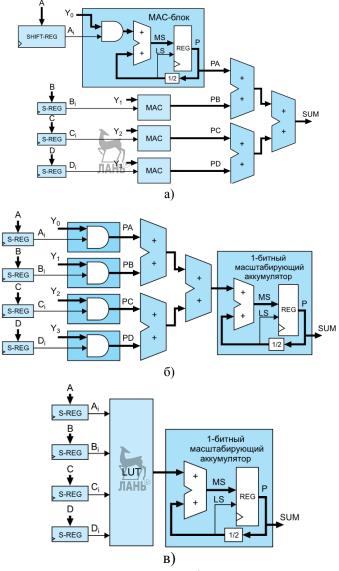

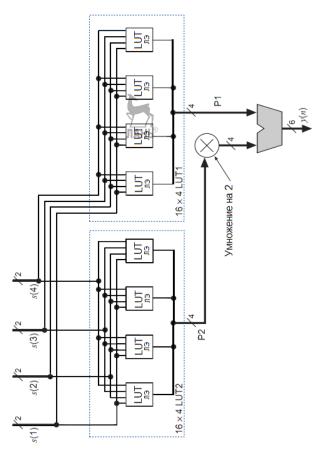

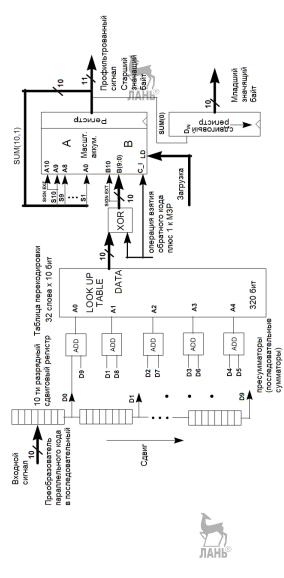

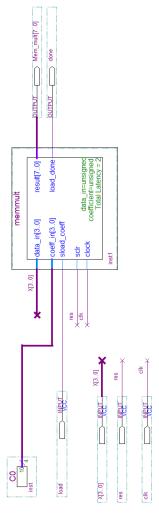

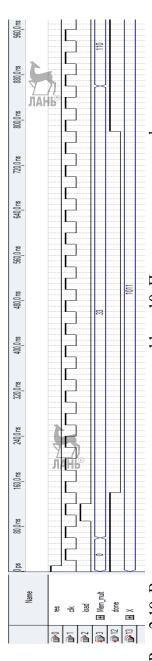

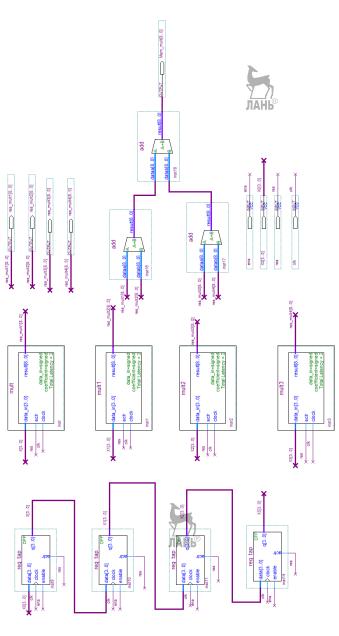

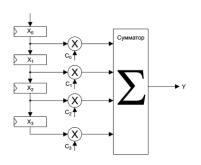

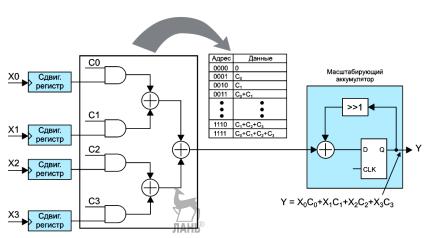

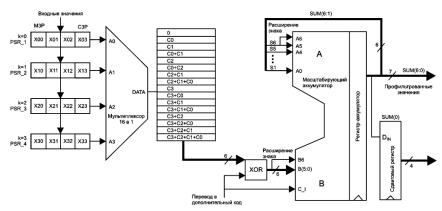

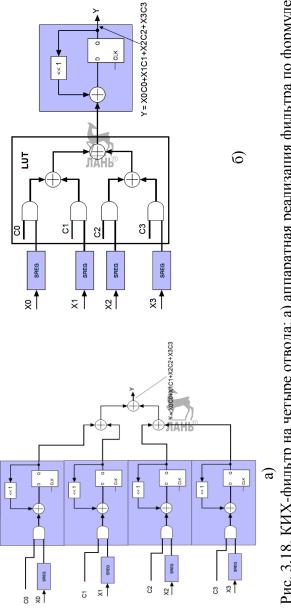

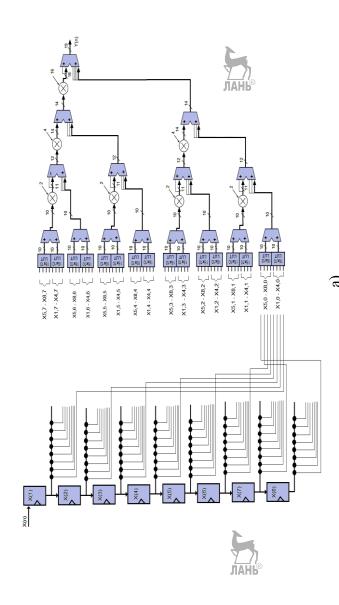

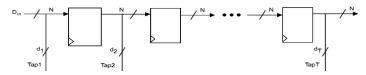

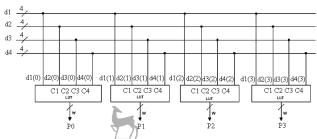

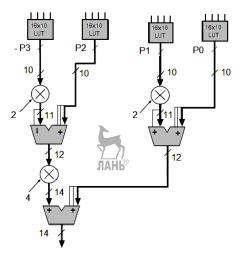

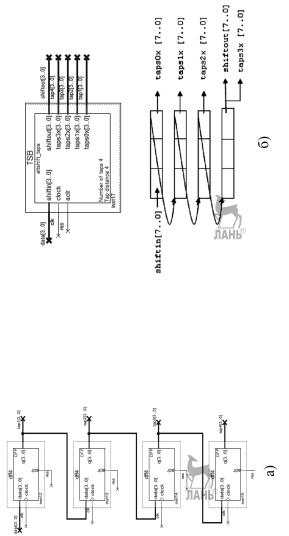

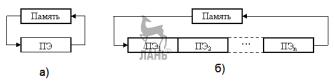

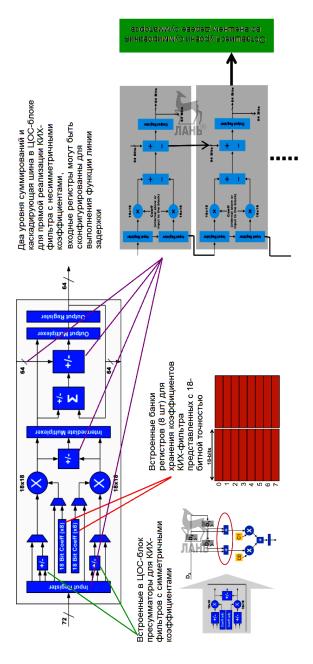

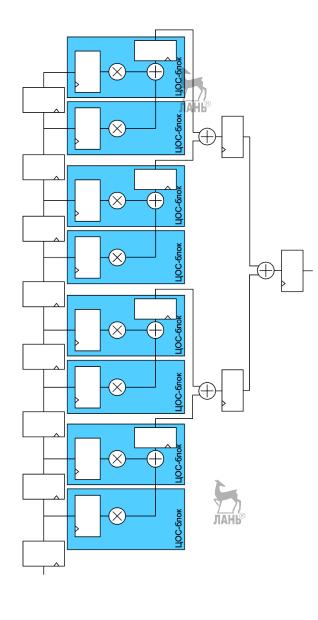

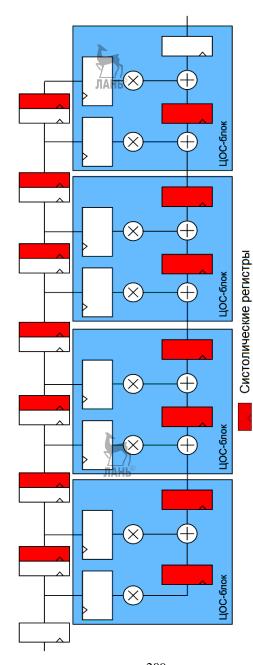

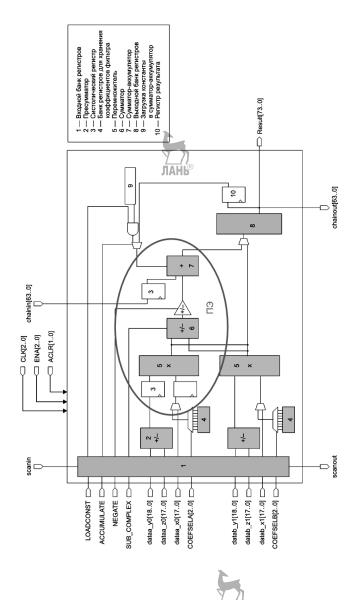

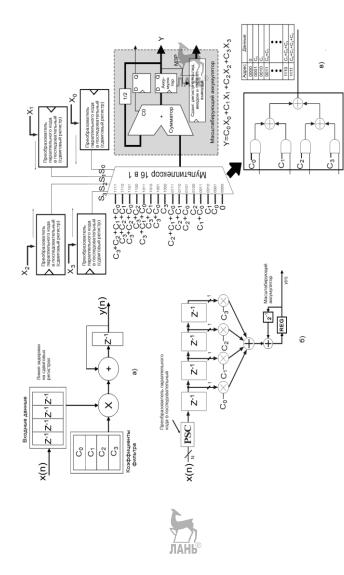

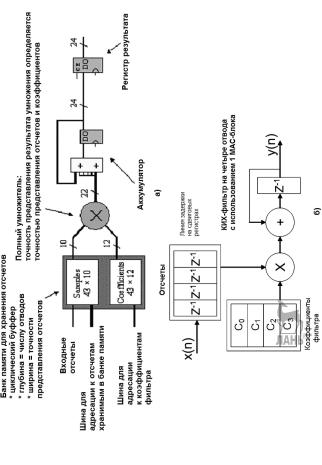

При реализации КИХ-фильтра на четыре отвода в базисе ЦОС-процессоров требуется четыре блока умножения с накоплением (рис. 1.7, а). Применение последовательной распределенной арифметики позволяет сократить используемых ресурсов за счет использования составных частей МАС-блока. Это четыре блока логики генерации частичных произведений, получаемых применением булевой операции логическое И к множимому (многоразрядные константы, являющиеся коэффициентами фильтра) и битовому значению множителя с выходов линии задержки, а также единственный масштабирующий аккумулятор. дерево многоразрядных сумматоров не сокращается (рис. 1.7, б). При проектировании фильтра в базисе ПЛИС (рис. 1.7, в) на распределенной последовательной арифметике логика частичных произведений и их последующее суммирование с помощью дерева многоразрядных сумматоров

реализуются единственной таблицей перекодировки (LUT). Суммирование значений с выходов таблицы перекодировки осуществляется с использованием масштабирующего аккумулятора. Реализация КИХ-фильтров в базисе ПЛИС с использованием распределенной арифметики обеспечивает наивысшее быстродействие системы и наименьшее число используемых ресурсов проекта.

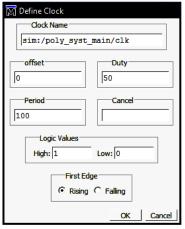

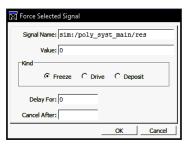

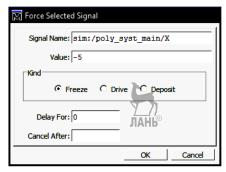

Рассмотрим проектирование МАС-блока с использованием Встраивание управляющего автомата. автомата схему позволяет получить готовую функцию без использования дополнительных управляющих сигналов для умножения двух четырехразрядных чисел без знака. По входам МАС-блока потребуются всего лишь три сигнала: сигнал асинхронного сброса res, сигнал тактирования clk и сигнал разрешения загрузки числа X (множителя) в сдвиговый регистр load\_PSC. Для корректной работы схемы необходимо обнулить все регистры умножителя (активный – высокий уровень сигнала res). Поскольку все регистры, в том числе и регистр для хранения состояний в управляющем автомате обнуляются лишь перед началом работы единожды, то для упрощения разработки процесса схемы онжом воспользоваться асинхронным сбросом.

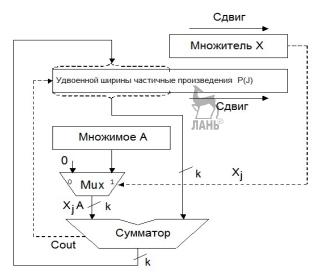

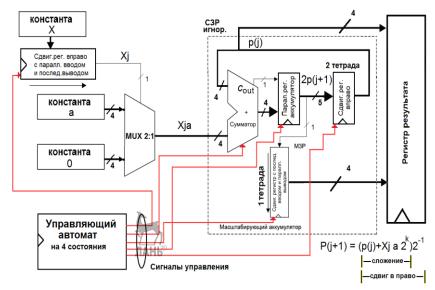

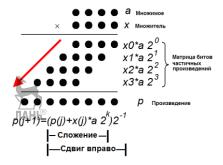

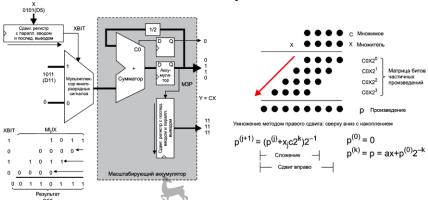

Принцип умножения методом правого сдвига и сложения показан на рис. 1.8. Идея схемы метода умножения методом правого сдвига с накоплением показана на рис. 1.9. На рис. 1.10 предлагается структурная схема метода умножения с использованием управляющего автомата.

Рис. 1.7. Миграция проекта КИХ-фильтра на четыре отвода: а) и б) реализация в базисе сигнальных процессоров; в) в базисе ПЛИС

|                                                            | Cou | t 2 тетрада                   | 1 тетрада        | 2 тетрада                              | 2 тетрада     | 1 и 2 тетрады |

|------------------------------------------------------------|-----|-------------------------------|------------------|----------------------------------------|---------------|---------------|

| a 10<br>X 11                                               |     |                               | 1 0 1 0 1 1      |                                        |               |               |

| $p^{(0)} + x_0 a$                                          |     | 0 0 0 0<br>1 0 1 0            | 0 0 0            | <sub>©</sub> 0<br>a                    | 0<br>10       |               |

| 2p <sup>(1)</sup><br>p <sup>(1)</sup><br>+x <sub>1</sub> a | 0   | 1 0 1 0<br>0 1 0 1<br>1 0 1 0 | 0 0 0 0          | a<br>a/2<br>a                          | 10<br>5<br>10 | 80            |

| 2p <sup>(2)</sup><br>p <sup>(2)</sup><br>+x <sub>2</sub> a | 0   | 1 1 1 1<br>0 1 1 1<br>0 0 0 0 | 0 1 0 0 0        | a/2+a<br>(a/2+a)/2<br>0                | 15<br>7<br>0  | 120           |

| 2p <sup>(3)</sup><br>p <sup>(3)</sup><br>+x <sub>3</sub> a | 0   | 0 1 1 1<br>0 0 1 1<br>1 0 1 0 | 1 0<br>1 1 0 0   | (a/2+a)/2<br>((a/2+a)/2)/2<br>a        | 7<br>3<br>10  | 60            |

| 2p <sup>(4)</sup><br>p <sup>(4)</sup>                      | 0   | 1 1 0 1<br>0 1 1 0            | 1 1 0<br>1 1 1 0 | ((a/2+a)/2)/2+a<br>(((a/2+a)/2)/2+a)/2 | 13<br>6       | 110           |

Рис. 1.8. Принцип умножения методом правого сдвига и сложения. Умножение десятичного числа 10 на десятичное число 11

Рис. 1.9. Структурная схема умножителя методом правого сдвига и сложения

Рис. 1.10. Предлагаемая структурная схема умножителя с управляющим автоматом

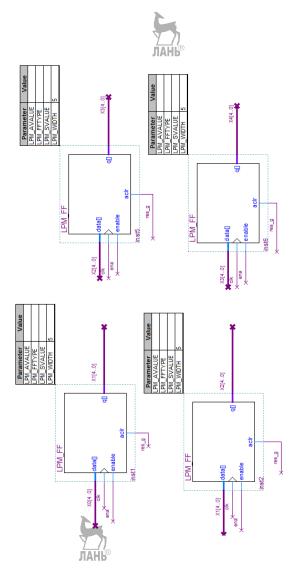

Структурная схема умножителя двух 4-разрядных чисел, представленных в двоичном коде (целые, положительные числа), состоит из шинного мультиплексора 2 в 1, сдвигового цифрового автомата Гна четыре состояния регистра, масштабирующего аккумулятора Дрис. 1.11). мультиплексор 2 в 1 и сдвиговый регистр вправо реализуют генерации произведений. В частичных масштабирующего аккумулятора лежит синхронизируемый сумматор с сигналом разрешения тактирования (рис. 1.12).

### LIBRARY ieee; USE ieee.std\_logic\_1164.all; USE ieee.std\_logic\_unsigned.all; ENTITY avtomat IS PORT(

```

Res,clk: IN

STD_LOGIC;

Ena Add, LoadPSC, ena shift, Stop: OUT

STD LOGIC;

: OUT STD LOGIC VECTOR(4 downto 0));

END avtomat;

ARCHITECTURE a OF avtomat IS

TYPE state_values IS (SA, SB, SC, SD);

signal state,next_state: state_values;

SIGNAL cnt: STD LOGIC VECTOR(4 downto 0);

BEGIN

statereg: process(clk,Res)

begin

if (Res = '1') then state\leq SA;

elsif (clk'event and clk='1') then

state<=next_state;

end if:

end process statereg;

process(state)

begin

case state is

when SA=> next_state<=SB;

when SB=> next_state<=SC;

when SC=> next state<=SD;

when SD=> next state<=SA;

end case;

end process;

process (state)

begin

case state is

when SA=>Ena Add<='0';

LoadPSC<='0'; ena_shift<='1';

when SB=>

Ena Add<='1'; LoadPSC<='0';

ena shift<='0';

when SC=>

Ena Add<='0';

LoadPSC<='0';

```

```

ena_shift<='0';

when SD=>

Ena Add<='0':

LoadPSC<='1':

ena shift<='1';

end case:

end process;

process (clk, res)

begin

if (res = '1') then

cnt <=(others=>'0');

elsif (clk'event and clk = '1') then

if cnt = "10001" then Stop <= '1';

else cnt \leq cnt+'1';

end if:

end if:

end process;

Oa \le cnt;

END a:

```

состояния

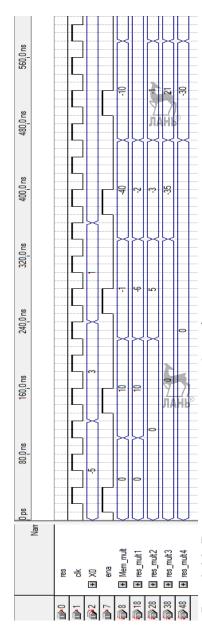

Цифровой автомат представляет собой автомат Мура на четыре состояния (SA (первое состояние), SB (второе состояние), SC (третье состояние) и SD (четвертое состояние)) и формирует три управляющих сигнала ena\_add\_temp, load\_acc и ena\_shift\_temp по срезу фронта синхроимпульса clk (пример).

Пример. Код языка VHDL управляющего автомата на четыре

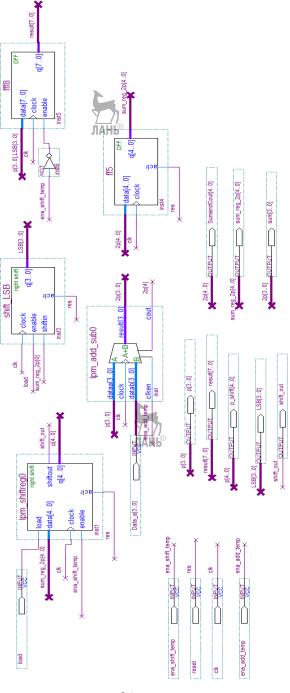

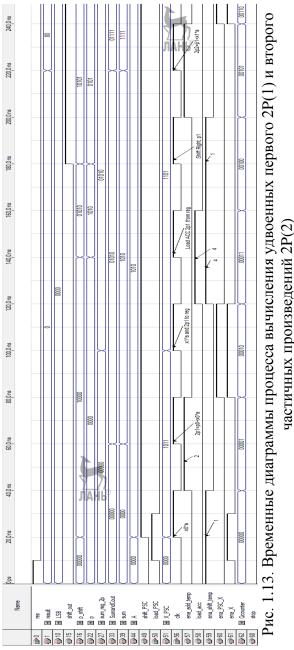

которых (ena\_add\_temp, load\_acc) Два ИЗ перекрывающиеся (рис. 1.13). По активному уровню сигнала асинхронного сброса res автомат попадает в первое состояние SA, по низкому уровню res осуществляется переход по состояниям. На рис. 1.13 над сигналами ena\_shift\_temp и load асс нанесены номера состояний цифрового автомата. Так, ena shift temp сигнал активен В первом четвертом И состояниях.

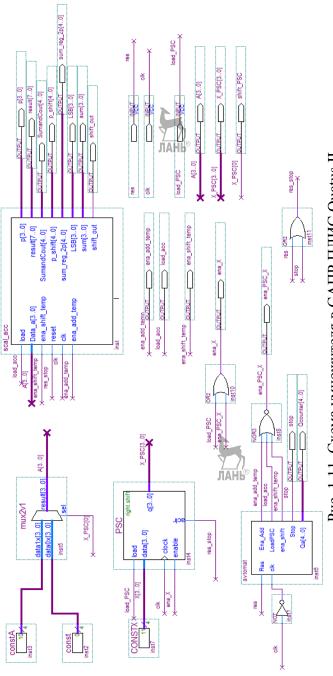

Рис. 1.11. Схема умножителя в САПР ПЛИС Quatus II

Рис. 1.12. Схема масштабирующего аккумулятора

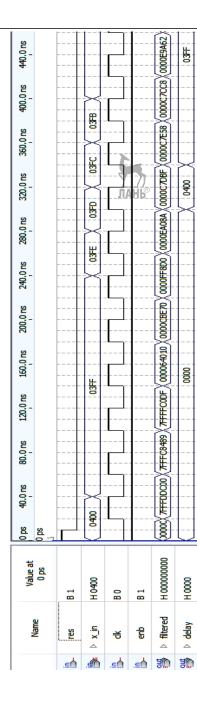

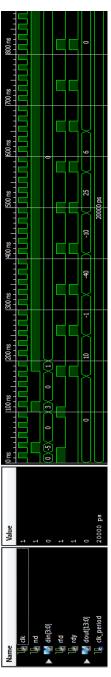

Рис. 1.14. Временные диаграммы процесса вычисления удвоенного четвертого частичного

произведения 2P(4)

Сигнал ena\_add\_temp формируется, когда автомат состоянии SB. Сигнал втором load acc находится во формируется в четвертом состоянии. Таким образом, удается обеспечить конвейерный режим работы масштабирующего аккумулятора, при этом формируемые сигналы ena\_add\_temp, load\_acc и ena\_shift\_temp являются синхронными для всех умножителя. Так, второй передний синхроимпульса оказывается ровно над половиной высокого уровня сигнал ena\_add\_temp. Что обеспечивает корректную работу синхронного сумматора (рис. 1.13). Четвертый передний фронт также оказывается ровно над половиной высоких уровней сигналов load\_acc и ena\_shift\_temp. Что обеспечивает загрузку числа с промежуточного регистра (аккумулятора) в сдвиговый регистр lpm\_shiftreg0. Пятый фронт также оказывается ровно над серединой высокого уровня сигнала ena\_shift\_temp для выполнения операции деления на 2 (сдвиг вправо).

В управляющий автомат встроен суммирующий счетчик, который подсчитывает число синхроимпульсов. И при достижении 18 (отсчет ведется с нуля) синхроимпульса вырабатывается сигнал остановки работы умножителя, который сбрасывает все регистры умножителя в ноль, кроме регистра результата (fff8), запись информации в который осуществляется низким уровнем сигнала ena\_shift\_temp.

информационные Ha входы мультиплексора (число подключаются лве константы. Множимое А) и логический адресный вход мультиплексора ноль. Ha младший разряд (множителя) подключается сдвигового регистра (мегафункция LPM\_SHIFTREG) с параллельным вводом информации и последовательным выводом. Такой (преобразователь регистр будем называть конвертор параллельного кода в последовательный) и обозначать как PSC. Регистр настроен на сдвиг вправо и имеет синхронные сигналы загрузки load и разрешения тактирования enable активные высоким уровнем. При сдвиге вправо в старший

разряд заносится логическая 1, а младший разряд теряется. В сдвиговый регистр по высокому уровню сигнала load PSC записывается число X (множитель). При этом сигнал ena X на входе enable должен быть высокого уровня, который может быть получен объединением по ИЛИ сигналов load PSC и ena PSC X. Сигнал ena PSC X является выходом цифрового автомата и получается применением операции ЗИЛИ-НЕ над сигналами ena add temp, load acc и ena shift temp, т.е. он возникает только в том случае, когда сигналы ena add temp, load acc и ena shift temp низкого уровня. В первом такте синхроимпульса сигнал ena PSC X не активен и не оказывает влияния на формирование сигнала епа X и используется при последующем сдвиге множителя Х вправо. Параллельная загрузка числа Х происходит по принципу: если активен сигнал загрузки load PSC, то, значит, должен быть активен и сигнал разрешения тактирования епа Х.

Недостатком такого решения является неразрешенный пятиразрядным сдвиговым регистром СЛВИГ вправо (lpm shiftreg0) масштабируемого аккумулятора при первом фронте синхроимпульса, на выходах которого появляется 1 в старшем разряде при активном сигнале ena shift temp, что и демонстрирует рис. 1.13. Однако это не влияет на работу масштабирующего аккумулятора, перед T.K. сдвиговый регистр перегружается правильным значением по четвертому фронту синхросигнала при активных сигналах ena shift temp. Неразрешенный load acc сдвиг проявляться последующих синхроимпульсах при при активного уровня сигнала ena shift temp. Для противодействия этому явлению старший значащий разряд p[4] регистра lpm shiftreg0 после сдвига просто игнорируется, а на вход сумматора поступает уменьшенное на два значение частичного произведения р[3..0] 4-битной c точностью представления.

Рассмотрим работу масштабирующего аккумулятора. По первому фронту синхроимпульса clk при активных

сигналах load\_PSC и ena\_X происходит загрузка числа X в сдвиговый регистр. По второму фронту синхроимпульса управляющий автомат вырабатывает синхронный тактирования ena\_add\_temp разрешения ДЛЯ сумматора масштабирующего аккумулятора. На выходах сумматора формируется первое удвоенное частичное произведение 2P(1)=P(0)+X(0)\*A (шина 2p[3..0]), равное 10 при этом P(0)=0. переноса Cout И 2P[3..0] объединяются пятиразрядную шину, значения которой сохраняются промежуточном параллельном регистре-аккумуляторе (выход sum reg 2p[4..0]) по третьему фронту синхроимпульса.

По четвертому фронту синхроимпульса при активных сигналах load\_acc и ena\_shift\_temp происходит первого удвоенного частичного произведения равного десяти в сдвиговый регистр. По пятому фронту при активном сигнале ena\_shift\_temp происходит вправо сдвиг удвоенного частичного произведения 2P(1). При этом выходах на сдвигового регистра образуется число 5. По шестому фронту ena add temp синхроимпульса при активном сигнале произойдет сложение числа А (десятичное число 10) с числом 5 и на выходах сумматора сформируется второе частичное произведение 2P(2) + P(1) + X(1) \* A равное числу 15. Что в соответствует точности принципу умножения, продемонстрированному на рис. 1.8.

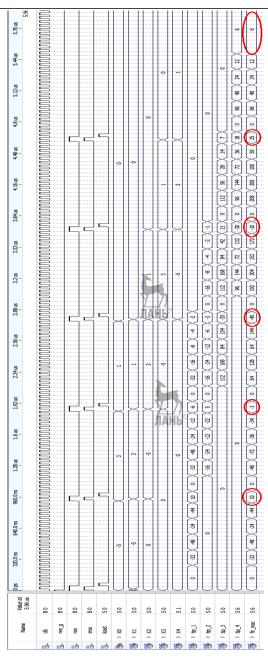

На рис. 1.14 показан момент окончания счета. По 15-му фронту синхроимпульса (отсчет по тексту ведется с 1-го фронта синхроимпульса) произойдет неразрешенная загрузка четвертого бита в сдвиговый регистр PSC по высокому уровню сигнала ena\_PSC\_X и сформируется еще одна копия сигнала А т.е. X(4)\*А. Однако это тоже не повлияет на результат, т.к. последующего сложения уже не будет. Потребуются еще два такта синхроимпульса для загрузки удвоенного произведения 2P(4) в аккумулятор и последующий сдвиг вправо для формирования P(4). И по 18-му такту импульса результат умножения будет доступен в регистре результата fff8.

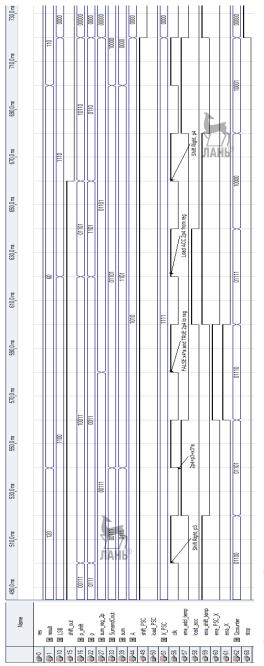

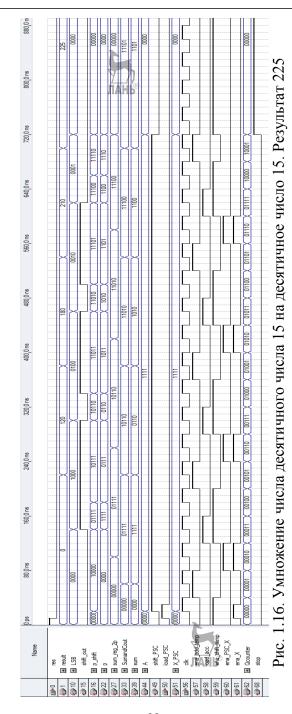

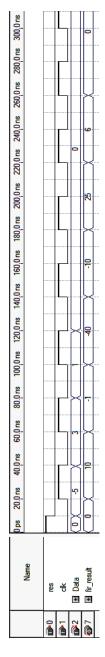

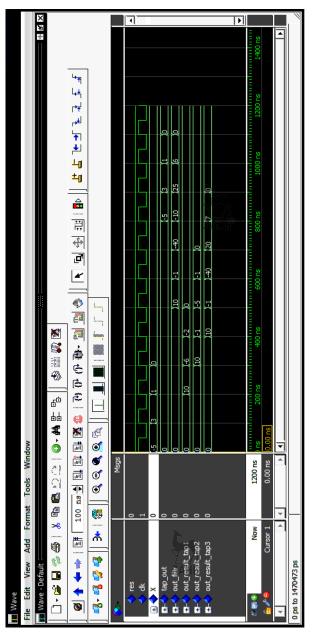

Было проведено тестирование разработанной схемы на предмет умножения двух 4-разрядных чисел без знака в диапазоне входных значений от 0 до 15. На рис. 1.15 показан принцип умножения десятичного числа 15 на 15, а на рис. 1.16 представлены временные диаграммы процесса умножения.

|                                                               | Cou       | <i>†</i> 2 тетрада              | 1 тетрада | 1 и 2 тетрадь |

|---------------------------------------------------------------|-----------|---------------------------------|-----------|---------------|

| a<br>X                                                        |           | 1111<br>1111                    |           |               |

| p <sup>(0)</sup><br>+x <sub>0</sub> a                         | _         | 0000<br>1111                    |           |               |

| $ \begin{array}{c} 2p^{(1)} \\ p^{(1)} \\ +x_1a \end{array} $ | ZO<br>ЛАН | 0 1 1 1 1<br>0 1 1 1<br>1 1 1 1 | 1000      | 120           |

| 2p <sup>(2)</sup><br>p <sup>(2)</sup><br>+x <sub>2</sub> a    | 1         | 0 1 1 0<br>1 0 1 1<br>1 1 1 1   | 0100      | 180           |

| 2p <sup>(3)</sup><br>p <sup>(3)</sup><br>+x <sub>3</sub> a    | 1         | 1010<br>1101<br>1111            | 0010      | 210           |

| 2p <sup>(4)</sup><br>p <sup>(4)</sup>                         | 1         | 1100<br>1110                    | 0001      | 225           |

Рис. 1.15. Принцип умножения методом правого сдвига и сложения. Умножение десятичного числа 15 на десятичное число 15

Разработан МАС-блок ДЛЯ умножения ДВVX без разрядных чисел знака с использованием метода умножения и накопления. Управление блоком осуществляется цифрового автомата четыре на Предложенная схема реализации МАС-блока в базисе ПЛИС может быть использована при проектировании КИХ-фильтров.

## 1.5. Проектирование умножителя целых чисел со знаком методом правого сдвига и сложения в базисе ПЛИС

Рассмотрим пример проектирования последовательностного универсального умножителя целых чисел, представленных в дополнительном коде, методом правого сдвига и сложения (МАС-блок) в базисе ПЛИС.

В качестве базовой схемы разрабатываемого МАС-блока возьмем схему умножителя целых без знаковых чисел с управляющим автоматом на четыре состояния (раздел 1.3).

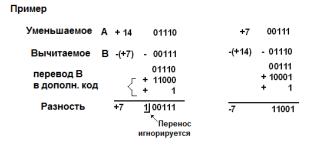

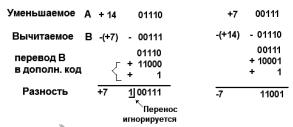

Рассмотрим умножение чисел со знаком в "столбик" (рис. 1.17). Дополнение до двух можно получить, если прибавить 1 к результату обращения. Обращение логически эквивалентно инверсии каждого бита в числе. Вентили Исключающее ИЛИ можно применить для избирательной инверсии в зависимости от значения управляющего сигнала. Прибавление 1 к результату обращения можно реализовать, задавая 1 на входе переноса сумматора.

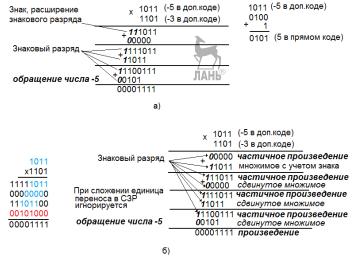

На рис. 1.18 показан принцип умножения чисел представленных дополнительным кодом, на примере умножения -5x-3.

Рис. 1.17. Вычитание с использованием дополнительного кода (дополнение до двух). Осуществляются инвертирование вычитаемого, суммирование и перенос 1 в младший разряд с последующим сложением

Рис. 1.18. Умножение в столбик (а); умножение методом сдвига множимого и последующего сложения с частичным произведением (умножение чисел -5x-3, представленных в дополнительном коде) (б)

Представление точечной процесса умножения нотации, в которой под каждой точкой подразумевается логический 0. логическая или позволяет получить рекуррентную формулу (рис. 1.19).

Рис. 1.19. Представление процесса умножения методом правого сдвига и сложения в точечной нотации

Ниже показаны примеры умножения, рассматриваемые при разработке схемы универсального умножителя.

| Случай 1.                  | Случай 2.                 |

|----------------------------|---------------------------|

| Множимое - отрицательное   | Множимое и множитель -    |

| число                      | отрицательные числа       |

| Множитель - положительное  | -10x-11                   |

| число                      |                           |

| -10x11                     |                           |

| Случай 3.                  | Случай 4.                 |

| Множимое и множитель -     | Множимое - положительное  |

| четные отрицательные числа | число                     |

| -4x-4                      | Множитель - отрицательное |

|                            | число                     |

|                            | 5x-3                      |

Множитель (11) — целое положительное число, расширенное знаковым разрядом 0, представлено в прямом коде. Для удвоенных частичных произведений 2p(1), 2p(2), 2p(3), 2p(4) и 2p(5) в поле MSB (название полей произвольное) необходимо добавить логическую 1. При формировании частичных произведений методом правого сдвига p(1), p(2), p(3), p(4) и p(5) логическая 1 из поля MSB попадает в старший разряд второй тетрады (название "тетрады" в данном случае некорректно, т.к. это поле уже 5-разрядное, но сохранено для приемлемости с принципом умножения без знаковых чисел).

При сложении p(3) с x3\*а единица переноса в старший разряд, т.е. в поле MSB, игнорируется. Данная схема вычислений справедлива только для случая, когда в младшем разряде множителя находится 1.

| ı                       | MSE | 3 2 тетрада                         | 1 тетрада    |

|-------------------------|-----|-------------------------------------|--------------|

| a(-10)<br>x(11)         |     | 10110<br>01011                      | ЛАНЬ®        |

| p(0)<br>+x0*a           |     | 00000<br>10110                      |              |

| 2p(1)<br>p(1)<br>+x1*a  | 1   | 10110<br>11011<br>10110             | 0            |

| 2p(2)<br>p(2)<br>+x2*a  | 1   | 10001<br>11000<br>00000             | 0 1 0        |

| 2p(3)<br>p(3)<br>+x3(a) |     | 1 1 0 0 0<br>1 1 1 0 0<br>1 0 1 1 0 | 1 0<br>0 1 0 |

| 2p(4)<br>p(4)<br>x4*a   | 1   | 10010<br>11001<br>00000             | 010<br>0010  |

| 2p5<br>p5               | 1   | 11001<br>11100                      | 0010         |

⊩

|                          | MSE | В 2 тетрада             | 1 тетрада     |

|--------------------------|-----|-------------------------|---------------|

| a(-10)<br>x(-11)         |     | 10110<br>10101          |               |

| p(0)<br>+x0*a            |     | 00000                   |               |

| 2p(1)<br>p(1)<br>+x1*a   | 1   | 10110<br>11011<br>00000 | o             |

| 2p(2)<br>p(2)<br>+x2*a   | 1   | 11011<br>11101<br>10110 | 0 1 0         |

| 2p(3)<br>p(3)<br>+x3(a)  | 1   | 10011<br>11001<br>00000 | 10<br>110     |

| 2p(4)<br>p(4)<br>(-x4*a) | 1   | 11001<br>11100<br>01010 | 110<br>1110   |

| 2p5<br>p5                | 0   | 00110<br>00011          | 1110<br>01110 |

б)

Рис. 1.20. Принцип умножения методом правого сдвига и сложения:

а) умножение -10х11; б) умножение -10х-11

При умножении двух отрицательных чисел, представленных дополнительным кодом (например, -10x-11), необходимо произвести два действия. Первое: необходимо учесть знак при представлении числа в дополнительном коде, что достигается обращением произведения старшего разряда множителя на множимое с последующим прибавлением 1 к младшему разряду. Дополнительный код произведения (-x4\*a) при x4=1 есть число 10. Перевод в дополнительный код произведения (-x4\*a) должен быть осуществлен до операции

сложения, т.е. до получения удвоенного частичного произведения 2р(5).

Второе: при формировании удвоенного частичного произведения 2p(5) необходимо произвести коррекцию, т.е. в поле MSB поставить логический ноль.

Рассмотрим умножение четных чисел со знаком (рис. 1.21). При умножении -4x-4 в поле MSB для удвоенных значений частичных произведений 2p(1) и 2p(2) должны стоять нули. А при умножении -8x-8 нуль в поле MSB должен быть еще 0 и для частичного произведения 2p(3). Далее, принцип умножения не отличается от умножения чисел, представленных дополнительным кодом (например, -10x-11).

|                          | MS | В 2 тетрада             | 1 тетрада | _  |                          | MSI | В 2 тетрада             | 1 тетрада |

|--------------------------|----|-------------------------|-----------|----|--------------------------|-----|-------------------------|-----------|

| a (-4)<br>x(-4)          |    | 11100<br>11100          |           |    | a(-8)<br>x(-8)           |     | 11000<br>11000          |           |

| p(0)<br>+x0*a            |    | 00000                   |           |    | p(0)<br>+x0*a            |     | 00000                   |           |

| 2p(1)<br>p(1)<br>+x1*a   | 0  | 00000<br>00000<br>00000 | 0         |    | 2p(1)<br>p(1)<br>+x1*a   | 0   | 00000                   | o         |

| 2p(2)<br>p(2)<br>+x2*a   | 0  | 00000<br>00000<br>11100 | 0         |    | 2p(2)<br>p(2)<br>+x2*a   | 0   | 00000                   | 0         |

| 2p(3)<br>p(3)<br>+x3(a)  | 1  | 11100<br>11110<br>11100 | 00        | 1  | 2p(3)<br>p(3)<br>+x3(a)  | 0   | 00000<br>00000<br>11000 | 00        |

| 2p(4)<br>p(4)<br>(-x4*a) | 1  | 11010<br>11101<br>00100 | 000       | ЛА | 2p(4)<br>p(4)<br>(-x4*a) | 1   | 11000<br>11100<br>01000 | 000       |

| 2p5<br>p5                | 0  | 00001                   | 0000      |    | 2p5<br>p5                | 0   | 00100                   | 0000      |

|                          |    | a)                      | •         | -  |                          | _   | 6)                      | •         |

Рис. 1.21. Принцип умножения методом правого сдвига и сложения: а) умножение -4х-4; б) умножение -8х-8

На рис. 1.22 показан принцип умножения методом правого сдвига и сложения в случае, когда множимое – положительное, а множитель - отрицательное числа.

| /                        | MSI | В 2 тетрада             | 1 тетрада    |

|--------------------------|-----|-------------------------|--------------|

| a (5)<br>x (-3)          |     | 00101<br>11101          |              |

| p(0)<br>+x0*a            |     | 00000                   |              |

| 2p(1)<br>p(1)<br>+x1*a   | 0   | 00101<br>00010<br>00000 | 1            |

| 2p(2)<br>p(2)<br>+x2*a   | 0   | 00010<br>00001<br>00101 | 1 0 1        |

| 2p(3)<br>p(3)<br>+x3(a)  | 0   | 00110<br>00011<br>00101 | 0 1<br>0 0 1 |

| 2p(4)<br>p(4)<br>(-x4*a) | 0   | 01000<br>00100<br>11011 | 001          |

| 2p5<br>p5                | 1   | 11111                   | 0001         |

|                          | MSB 2 тетрада 1 тетрада |                         |               |  |  |  |  |

|--------------------------|-------------------------|-------------------------|---------------|--|--|--|--|

| a (2)<br>x (-2)          |                         | 00010                   |               |  |  |  |  |

| p(0)<br>+x0*a            |                         | 00000                   |               |  |  |  |  |

| 2p(1)<br>p(1)<br>+x1*a   | 0                       | 00000<br>00000<br>00010 | 0             |  |  |  |  |

| 2p(2)<br>p(2)<br>+x2*a   | 0                       | 00010<br>00001<br>00010 | 0 00          |  |  |  |  |

| 2p(3)<br>p(3)<br>+x3(a)  | 0                       | 00011<br>00001<br>00010 | 00<br>100     |  |  |  |  |

| 2p(4)<br>p(4)<br>(-x4*a) | 0                       | 00011<br>00001<br>11110 | 100<br>1100   |  |  |  |  |

| 2p5<br>p5                | 1                       | 11111                   | 1100<br>11100 |  |  |  |  |

Рис. 1.22. Принцип умножения методом правого сдвига и сложения: a) умножение 5x-3; б) умножение 2x-2

Разработанный МАС-блок также способен умножать числа без знака. Для этого применяется принцип, показанный на рис. 1.23. Единица переноса при сложении в поле "2 тетрада" уже не игнорируется, а переносится в поле Cout (сигнал Cout является выходом переноса многоразрядного сумматора масштабирующего аккумулятора).

|                                                            | Cou | <i>t</i> 2 тетрада            | 1 тетрада | 1 и 2 тетрадь |

|------------------------------------------------------------|-----|-------------------------------|-----------|---------------|

| a<br>X                                                     |     | 1 1 1 1<br>1 1 1 1            |           |               |

| p <sup>(0)</sup><br>+x <sub>0</sub> a                      |     | 0000<br>1111                  |           |               |

| $2p^{(1)}$ $p^{(1)}$ $+x_1a$                               | 0   | 1 1 1 1<br>0 1 1 1<br>1 1 1 1 | 1000      | 120           |

| 2p <sup>(2)</sup><br>p <sup>(2)</sup><br>+x <sub>2</sub> a | 1   | 0 1 1 0<br>1 0 1 1<br>1 1 1 1 | 0100      | 180           |

| 2p <sup>(3)</sup><br>p <sup>(3)</sup><br>+x <sub>3</sub> a | 1   | 1010<br>1101<br>1111          | 0010      | 210           |

| 2p <sup>(4)</sup>                                          | 1   | 1100<br>1110                  | 0001      | 225           |

Рис. 1.23. Принцип умножения методом правого сдвига и сложения. Умножение 15x15

Поскольку принципы умножения чисел со знаком и без знака отличаются, то необходимо откорректировать код языка VHDL цифрового автомата (пример). В коде содержатся шесть операторов process, которые выполняются параллельно.

LIBRARY ieee;

USE ieee.std\_logic\_1164.all;

USE ieee.std\_logic\_unsigned.all;

**ENTITY** avtomat IS

PORT(

Res,clk: IN STD\_LOGIC;

X,A: IN STD\_LOGIC\_VECTOR(4 downto 0);

Ena Add, LoadPSC, ena shift, Stop, sub add, sign: OUT STD LOGIC;

Q\_sub\_add : OUT STD\_LOGIC\_VECTOR(4 downto 0);

Q stop : OUT STD LOGIC VECTOR(4 downto 0));

END avtomat;

ARCHITECTURE a OF avtomat IS

```

TYPE state_values IS (SA, SB, SC, SD);

signal state, next state: state values;

SIGNAL cnt_sub_add: STD_LOGIC_VECTOR(4 downto 0);

SIGNAL cnt_stop: STD_LOGIC_VECTOR(4 downto 0);

BEGIN

statereg: process(clk,Res)

begin

if (Res = '1') then state\leq SA;

elsif (clk'event and clk='1') then

state<=next_state;

end if;

end process statereg;

process(state)

begin

case state is

when SA=> next state<=SB;

when SB=> next_state<=SC;

when SC=> next state<=SD;

when SD=> next state<=SA;

end case:

end process;

process (state)

begin

case state is

when SA=>Ena Add<='0';

LoadPSC<='0';

ena shift<='1';

when SB=>

Ena Add<='1';

LoadPSC<='0':

ena shift<='0';

when SC=>

Ena Add<='0';

LoadPSC<='0';

ena_shift<='0';

when SD=>

Ena Add\leq='0';

LoadPSC<='1':

```

```

ena_shift<='1';

end case:

end process;

process (clk, res)

begin

if (res = '1') then cnt sub add <=(others=>'0');

elsif (clk'event and clk = '0') then

cnt_sub_add <= cnt_sub_add+'1';

end if:

end process;

Q_sub_add <= cnt_sub_add;

process(cnt sub add,X,A)

begin

-- Случай 4

if A(4)='0' and X(4)='1' then

sign<='1'; sub_add<='0';

case cnt_sub_add is

when "10001" =>

sign<='0'; sub add<='1';

when "10010" =>

sign<='1'; sub_add<='1';

when others \Rightarrow sign\leq1'; sub_add\leq0';

end case:

-- Для случаев 1,2 и 3

elsif A(4)='1' then

case cnt sub add is

when "00010" =>

if (X(0)='0') then sign<='1'; sub_add<='0'; else

sign<='0'; sub_add<='0'; end if;

when "00110" =>

if (X(1)='0' \text{ and } X(0)='0') then sign<='1'; sub_add<='0'; else sign<='0';

sub_add<='0'; end if;

when "01010" =>

if (X(2)=0') and X(1)=0' and X(0)=0') then sign<='1'; sub_add<='0'; else

sign<='0'; sub_add<='0'; end if; \( \)

when "01110" =>

if (X(3)=0') and X(2)=0' and X(1)=0' and X(0)=0' then sign<=1';

sub add<='0'; else sign<='0'; sub add<='0'; end if;

```

```

when "10001" =>

--2S complement else no 2S complement

if (X(4)='1') then sign<='1'; sub_add<='1'; else

sub_add<='0';sign<='0';end if;

when "10010" =>

----2S complement and 2p[5]=0 else no 2S complement and 2p[5]=1

if (X(4)='1')

or (X(4)=0') and X(3)=0' and X(2)=0' and X(1)=0' and X(0)=0'

then sign<='1'; sub add<='0'; else sub add<='0'; sign<='0'; end if;

when others \Rightarrow sign\leq '0';

sub add<='0';

end case:

end if:

end process;

process (clk, res)

begin

if (res = '1') then cnt_stop <=(others=>'0');

elsif (clk'event and clk = '1') then

if cnt stop = "10101" then Stop<='1';

else cnt stop <= cnt stop+'1';

end if:

end if:

end process;

Q_stop <= cnt_stop;

END a:

```

Пример. Код языка VHDL-цифрового автомата умножителя методом правого сдвига и сложения

Первые три оператора process реализуют цифровой автомат Мура на четыре состояния с логикой переходов и логикой формирования выхода для управления процессом умножения. Память состояний (регистр состояний) автомата тактируется фронтом синхроимпульса. Надо принимать во синхровход автомата clk внимание, что на подключен инвертор. Автомат формирует три управляющих сигнала ena add temp (сигнал разрешения суммирования сумматору масштабирующего многоразрядному

аккумулятора), load\_acc (сигнал разрешения загрузки в регистр со сдвигом вправо) и ena\_shift\_temp (сигнал разрешения сдвига) (рис. 1.24).

Четвертый оператор process представляет собой 5разрядный суммирующий счетчик на сигнале cnt sub add (тактируется срезом синхроимпульса clk'event and clk = '0'). образом удается обеспечить конвейерный режим работы масштабирующего аккумулятора, формируемые сигналы ena add temp, load acc и ena shift temp являются синхронными для всех регистров умножителя. Так, второй передний фронт синхроимпульса оказывается ровно над половиной высокого уровня сигнал ena add temp. Что работу обеспечивает корректную синхронного многоразрядного сумматора масштабирующего аккумулятора.

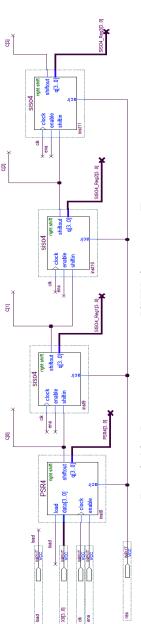

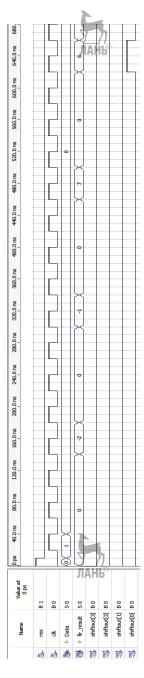

Согласно схемам на рис. 1.20-1.23 удвоенные частичные произведения 2p(1), 2p(2), 2p(3), 2p(4) и 2p(5) будут получены на 2, 6, 10 и 14 тактах сигнала ent sub add.

Пятый оператор process, в списке чувствительности которого стоит сигнал cnt\_sub\_add, используется как дешифратор случаев 4 и 1, 2 и 3. На сигнале cnt\_sub\_add осуществляется подсчет синхроимпульсов.

Рассмотрим подробно случай  $^{1}$ , 2 и 3 when "00010", "00110", "01010". Приведем примеры для множителя X: X=XXXX0 (например, 11110 BIN или -2D), X=XXX00 (например, 11100 BIN или -4D или же число со знаком -12, (10100 BIN), где четвертый разряд нулевой), X=XX000 (11000 BIN или -8D). X- или логическая 1 или логический 0. В случае обнаружения этих чисел цифровой автомат сформирует два сигнала sign<='1' и sub\_add<='0' для того, чтобы в поле MSB (2p[5]) установился логический 0. В этих случаях умножение идет согласно принципу, показанному на рис. 1.21.

Существует еще случай when "10001" когда будет подсчитан 17-й такт синхроимпульса, при достижении которого формируется двоичное дополнение. Это распространяется на умножение двух четных отрицательных

чисел и когда оба числа оказываются отрицательными, одно из которых может быть четное, а другое нечетное и наоборот.

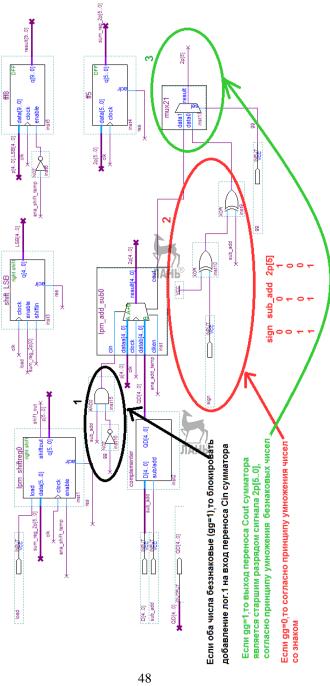

Сигнал sub\_add используется для подачи логической 1 на вход переноса многоразрядного сумматора Сіп масштабирующего аккумулятора, в случае обнаружения 1 в старшем разряде X(4)=1, а также для селективной инверсии числа A при переводе его в обратный код.

Когда будет подсчитан 18-й такт синхросигнала (when "10010"), цифровой автомат сформирует сигналы sign<='1' и sub add<='0' и в поле MSB будет установлен логический 0.

Шестой оператор process реализует схему останова процесса умножения на суммирующем счетчике тактируемым срезом синхроимпульса. При достижении 21-го синхроимпульса вырабатывается сигнал останова Stop.

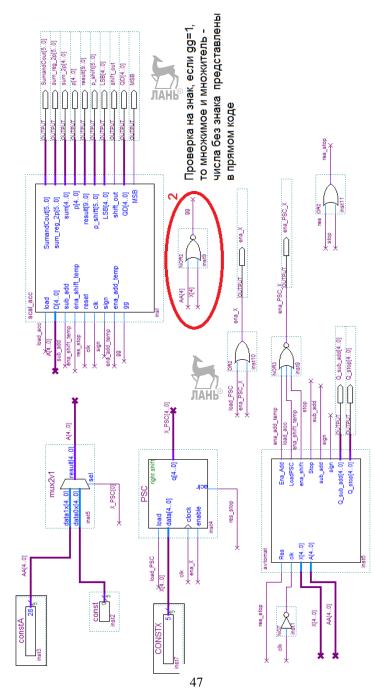

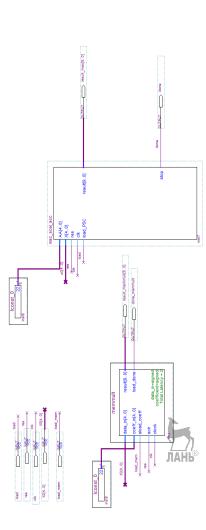

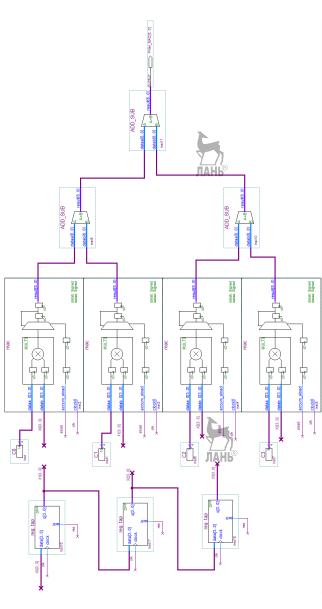

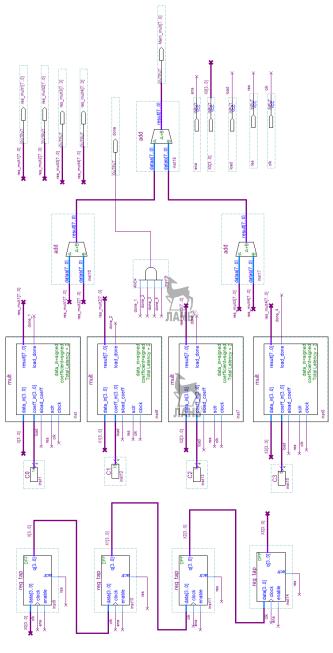

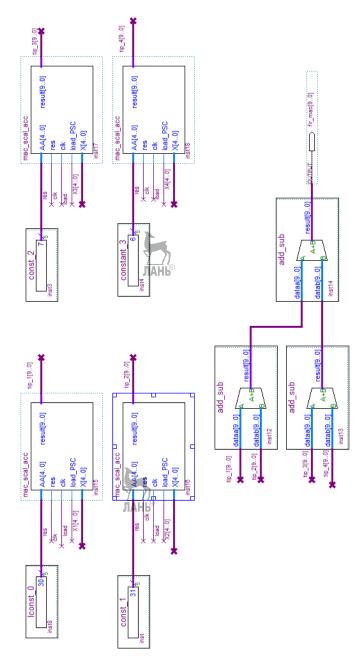

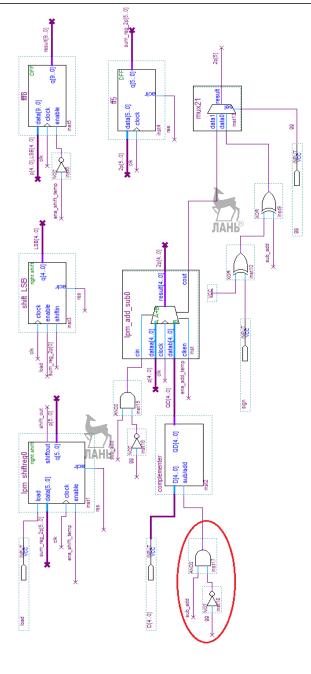

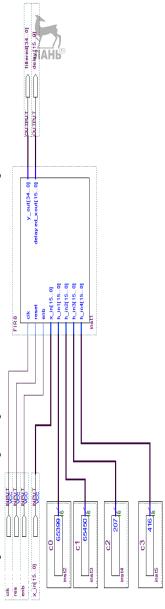

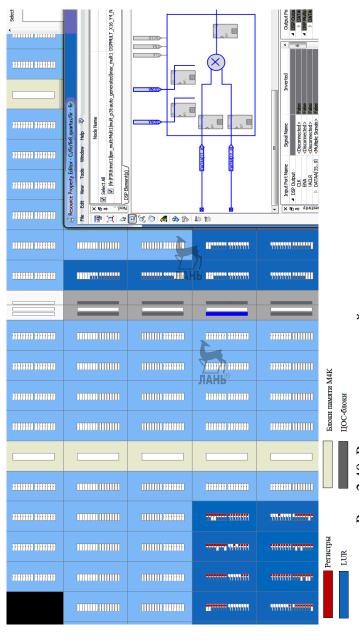

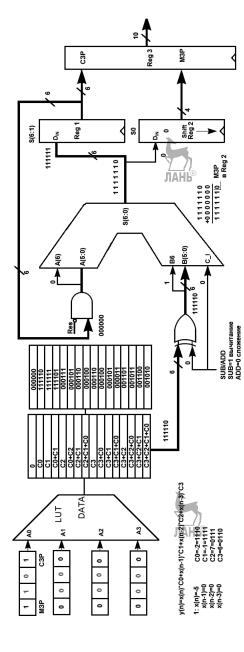

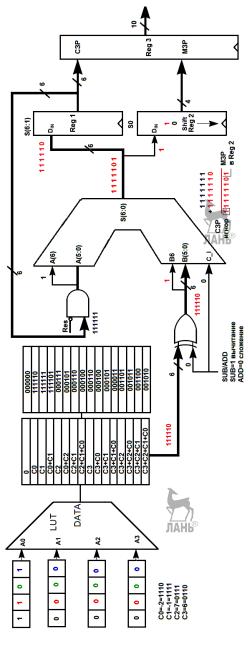

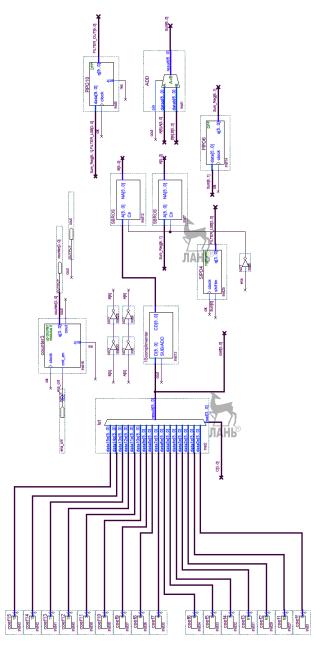

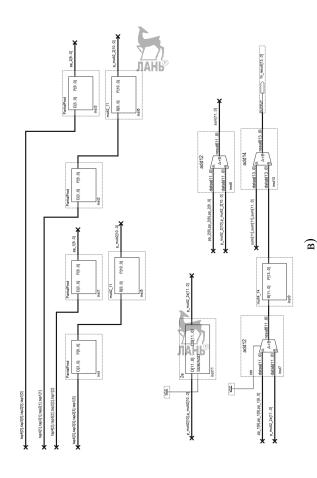

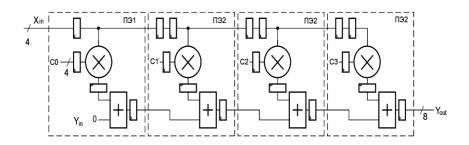

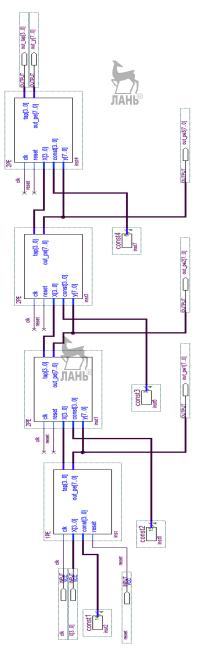

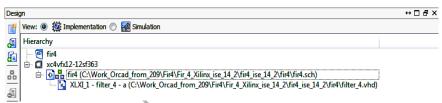

На рис. 1.24 и рис. 1.25 овалами под номерами один, два и три обведена дополнительная логика, обеспечивающая умножение чисел как со знаком, так и без. На рис. 1.24 показан уровень иерархии проекта универсального умножителя двух чисел в дополнительном коде как со знаком, так и без, в САПР ПЛИС Quatus II Web Edition 13.0.1sp1 (сборка 232). В отличие от схемы умножения беззнаковых чисел в схему введена дополнительная проверка на знак. Если сигнал gg = 1, то множимое A и множитель X - беззнаковые числа (выделен овалом под номером один). Блок complementer обеспечивает формирование обратного кола. переключения между без- и знаковыми числами обеспечивает мультиплексор mux21 (выделен овалом под номером два), на адресный вход которого подается сигнал gg. В целом принцип работы масштабирующего аккумулятора не отличается от аккумулятора ДЛЯ беззнаковых чисел за исключением увеличения разрядности всех блоков на 1 бит.

Поле MSB (рис. 1.25) формируется с помощью двух элементов "исключающее ИЛИ (XOR)". Вспомогательная схема выделена на рис. 1.25 овалом под номером три. Один из входов элемента XOR (inst10) подключен к напряжению

питания. Это необходимо для заполнения поля MSB логической 1 или логическим 0, как требуют случаи 1-4.

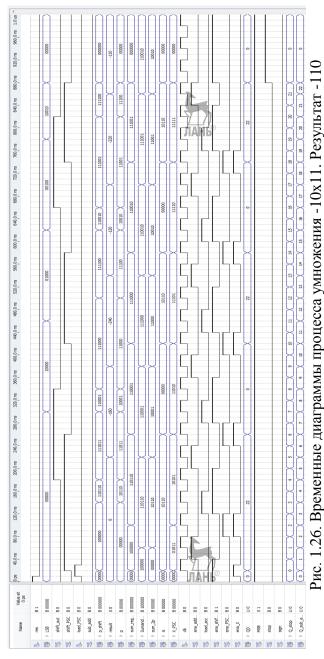

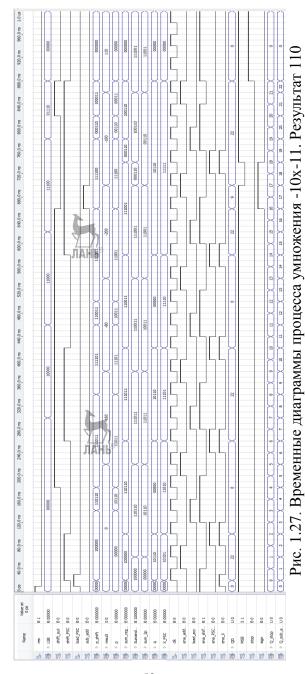

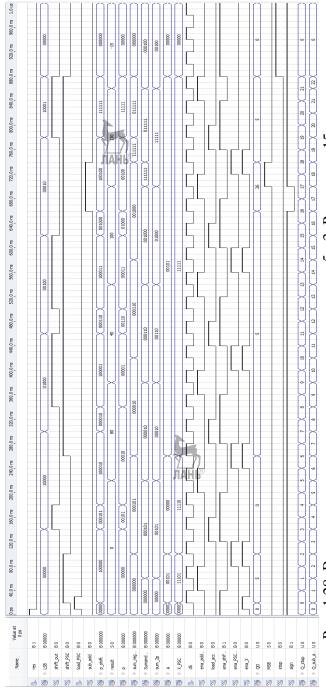

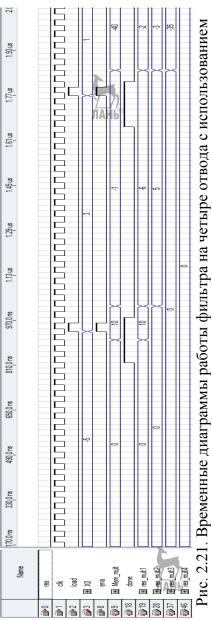

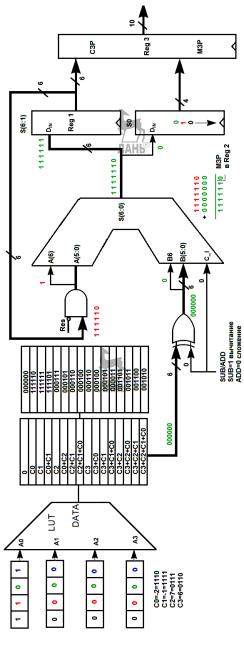

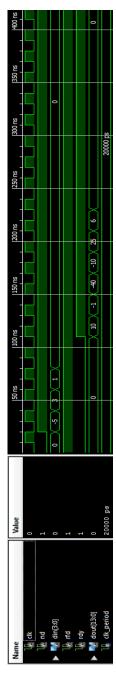

На рис. 1.26 и 1.27 показаны случаи 1 и 2, а на рис. 1.28 случай 4. В случае 1 в поле MSB в процессе умножения сохраняется логическая 1. В случае 2 в поле MSB при вычислении удвоенного частичного произведения 2p(5) прописывается логический 0 по 18-му такту синхроимпульса. В случае 4 в поле MSB все происходит с точностью наоборот.

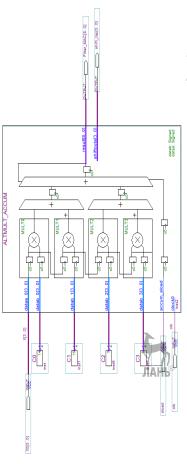

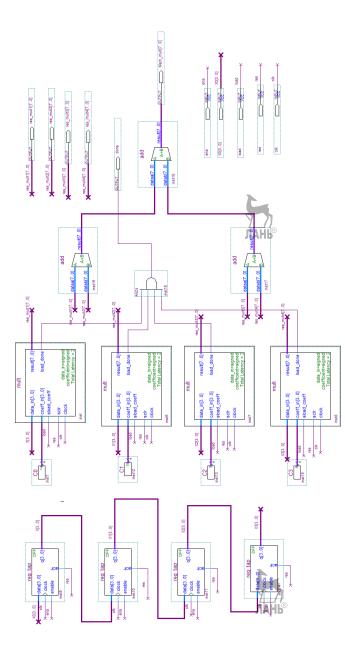

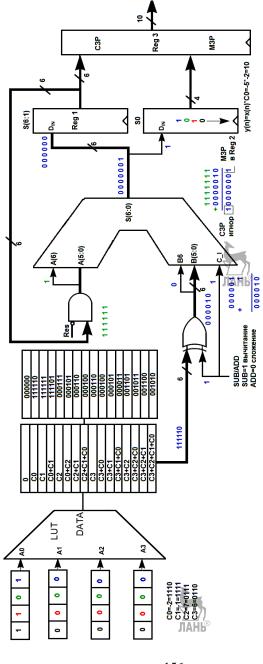

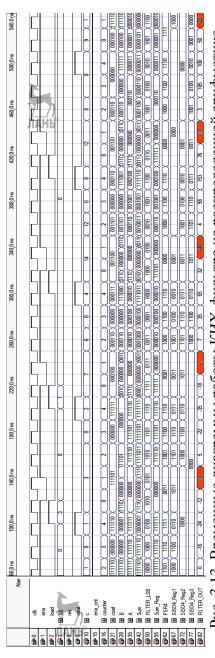

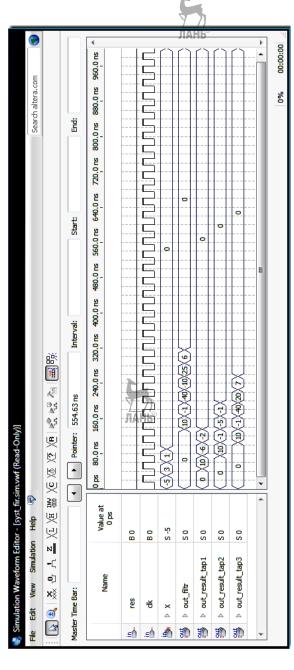

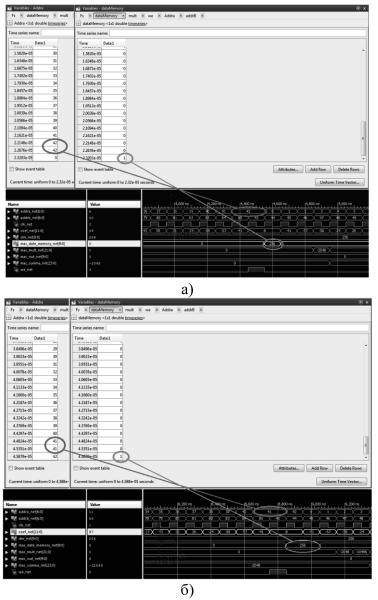

На рис. 1.29 показаны тестовые схемы для умножения -10x-11 для реализации в ПЛИС серии Cyclone II. На вход coeff in[4..0] мегафункции ALTMEMMULT подключается константа -10 (22D). Такое же значение подключается и на вход АА[4..0] разработанного МАС-блока (рис. 1.29). На  $data_in[4..0]$ информационный мегафункции вход ALTMEMMULT и на вход X[4..0] MAC-блока подается число -11. На рис. 1.30 показан процесс умножения -10x-11 MACслучая, мегафункцией для когда константа загружается внешнего порта. В мегафункцию предварительно загружена константа (режим загрузки блочной памяти ПЛИС) число 3.

Итак, данном разделе разработан МАС-блок использованием метода правого сдвига и сложения для умножения чисел, представленных в дополнительном коде как четных, так и нечетных, со знаком и без для реализации в базисе ПЛИС. Предложенная схема реализации МАС-блока 21 такт синхрочастоты быть за И может умножает использована при проектировании КИХ-фильтров.

Рис. 1.24. Схема умножителя в САПР ПЛИС Quatus II. Верхний уровень иерархии

Рис. 1.25. Схема масштабирующего аккумулятора

Рис. 1.28. Временные диаграммы процесса умножения 5х-3. Результат -15

Рис. 1.29. Тестирование мегафункции ALTMEMMULT и разработанного MAC-блока

мегафункцией ALTMEMMULT. Результат 110

## 1.6. Общие сведения по программным умножителям в базисе ПЛИС

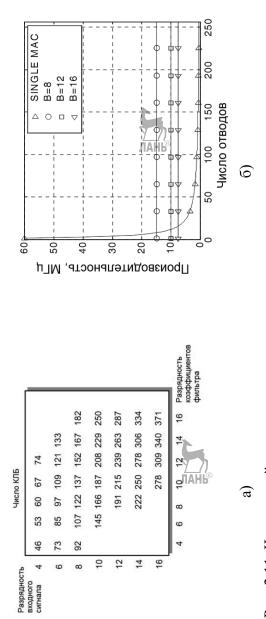

ПЛИС функциональных ДЛЯ повышения ИХ возможностей встраивают, например, для серии Cyclone III фирмы Altera аппаратные умножители, которые могут быть сконфигурированы в виде одного умножителя 18х18 либо в виде двух умножителей 9х9. Так, ПЛИС EP3CLS200 содержит 396 аппаратных умножителей 18х18, а на оставшихся ресурсах может быть реализован 891 программный умножитель 16x16. В итоге суммарное число умножителей составляет 1287 без какого-либо значительного использования логических ресурсов.

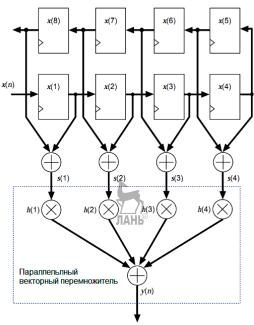

Для устройств цифровой обработки сигналов себя хорошо зарекомендовали софт-умножители (программные которые не требуют ресурсов умножители), аппаратных встроенных умножителей, В базис ПЛИС. Повысить производительность устройств цифровой обработки сигналов позволяет также использование параллельного векторного умножителя "безумножительных" схем использованием основ распределенной арифметики.

Рассмотрим параллельные программные умножители, способные произведение вычислять за один такт синхроимпульса, обеспечивая наивысшую производительность цифровой обработки сигналов. Программные умножители БИС программируемой логики (БИС ПЛ) фирмы Actel серий Fusion, IGLOO и ProASIC3 реализуются на блочной памяти меньшей размерности, чем у ПЛИС фирмы Altera и их можно рассматривать как 8-входовые LUT или таблицы произведений. Таблица произведений множимого, записанная во фрагмент блочной памяти, и называется LUT. Табл. показывает умножитель размерностью 1.2 3x3, реализованный с помощью 6-входовой LUT.

Таблица 1.2 Умножитель размерностью 3х3, реализованный с помощью 6-входовой LUT

## Множимое

Множитель

|          |     | 000    | 001    | 010    | 011    | 100    | 101    | 110    | 111    |

|----------|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| ٠ ا      | 000 | 000000 | 000000 | 000000 | 000000 | 000000 | 000000 | 000000 | 000000 |

|          | 001 | 000000 | 000001 | 000010 | 000011 | 000100 | 000101 | 000110 | 000111 |

| <u> </u> | 010 | 000000 | 000010 | 000100 | 000110 | 001000 | 001010 | 001100 | 001110 |

|          | 011 | 000000 | 000011 | 000110 | 001001 | 001100 | 001111 | 010010 | 010101 |

| ì        | 100 | 000000 | 000100 | 001000 | 001100 | 010000 | 010100 | 011000 | 011100 |

|          | 101 | 000000 | 000101 | 001010 | 001111 | 010100 | 011001 | 011110 | 100011 |

| •        | 110 | 000000 | 000110 | 001100 | 010010 | 011000 | 011110 | 100100 | 101010 |

|          | 111 | 000000 | 000111 | 001110 | 010101 | 011100 | 100011 | 101010 | 110001 |

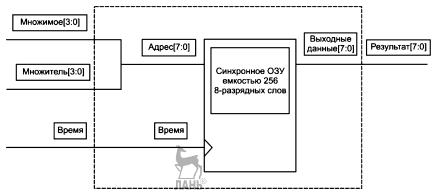

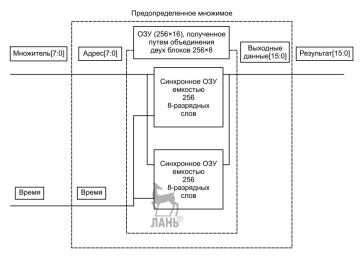

Например, у ПЛИС фирмы Actel используется ОЗУ емкостью 256 слов х 8 бит (256 8-разрядных слов), а у ПЛИС фирмы Altera может использоваться память М4К, которая может быть сконфигурирована, как 128 слов х 36 бит или 256 слов х 18 бит для серии Cyclone II. Такие умножители получили название RAM-LUT-умножители или LUT-based умножители.

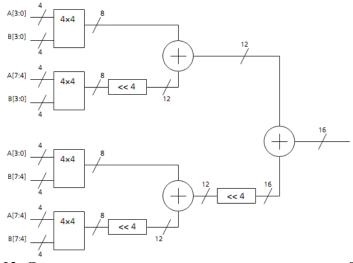

На рис. 1.31 показан умножитель 4х4 на базе синхронного ОЗУ емкостью 256 8-разрядных слов. Множимое (младшие четыре разряда адресной шины) и множитель (старшие четыре разряда адресной шины), представленные 4-разрядным двоичным кодом, объединяются в 8-разрядную адресную шину, адресуя своим уникальным кодом содержимое конкретной строки ОЗУ (операнды), являющееся 8-разрядным произведением.

Недостатком умножителя такого является резкое возрастание требуемого объема блочной памяти в случае увеличения его разрядности. Для умножителя размерностью 8х8 требуется 65536 16-разрядных слов. Поэтому чтобы предотвратить рост требуемой памяти практике на используется умножитель суммировании на частичных произведений в соответствии со своим весом (partial product multipliers).

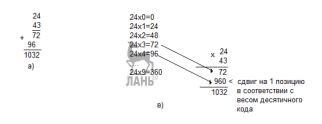

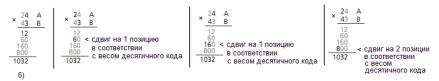

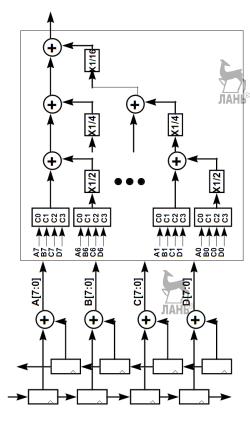

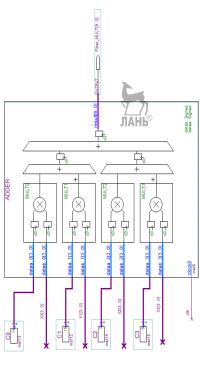

На рис. 1.32 показан пример умножения десятичного числа 24 на 43. Например, произведению 2 на 4 приписывается вес 100, что равносильно сдвигу на две позиции в десятичной системе. В этом случае необходим умножитель размерностью 8х8. Однако согласно принципу умножения с использованием частичных произведений требуются четыре умножителя размерностью 4х4 для формирования четырех частичных произведений И три сумматора: (4x3+((2x3)x10))+((4x4)+((2x4)x10)x10)=1032.1.33 Ha рис. показана структурная схема такого умножителя. Также для сдвига на одну и две десятичные позиции потребуются три сдвиговых регистра на четыре разряда влево дополнительные блоки, выполняющие операции расширения знака со значением старшего разряда.

Рис. 1.31. Программный умножитель размерностью 4x4 на базе ОЗУ емкостью 256 8-разрядных слов (256x8) фирмы Actel

Рис. 1.32. Принцип умножения: а) "в столбик" по правилу умножения десятичных чисел; б) с использованием частичных произведений; в) умножение на константу

Рис. 1.33. Структурная схема умножителя размерностью 8x8 с использованием четырех умножителей размерностью 4x4

Рассмотрим программные умножители на константу. Одна из наиболее распространенных операций цифровой обработки сигналов - умножение числа на константу. Для

перемножения двух чисел достаточно иметь таблицу произведений множимого (константы) на весь ранг возможных цифр множителя (табл. 1.3) и осуществить корректное суммирование полученных частичных произведений (рис. 1.32, в).

Таблица 1.3 Умножение 4-разрядного числа на константу 24 (рис. 1.32, в)

| Входы |      |      | X[  | [3] |

|-------|------|------|-----|-----|

| X[2]  | X[1] | X[0] | 0   | 1   |

|       | 000  |      | 0   | 192 |

|       | 001  |      | 24  | 216 |

| 010   |      |      | 48  | 240 |

|       | 011  |      | 72  | 264 |

| 100   |      |      | 96  | 288 |

|       | 101  |      | 120 | 312 |

|       | 110  |      | 144 | 336 |

| 111   |      |      | 168 | 360 |

Программные умножители фирмы Actel реализуются на 8-входовых LUT. Множимое (константа) в этом случае предопределено. В этом случае необходимы два блока памяти емкостью 256 8-разрядных слов позволяющих организовать массив памяти 256 16-разрядных слов из двух блоков емкостью 256 8-разрядных слов, выходная шина которого и есть 16-разрядный результат умножения двух 8-разрядных чисел (рис. 1.34).

Программные умножители фирмы Altera. Наличие встроенной блочной памяти TriMatrix<sup>тм</sup> в ПЛИС фирмы Altera, например, типа М9К используемой в качестве LUT, в которых хранятся частичные произведения, позволяет реализовывать параллельные умножители, экономя при этом не только аппаратные умножители, но и ресурсы логических

блоков. Наличие программных и аппаратных умножителей приводит в целом к увеличению общего числа возможных умножителей.

Рис. 1.34. Программный умножитель размерностью 8х8 числа на константу на базе ОЗУ емкостью 256 16-разрядных слов фирмы Actel

Использовать программные и аппаратные умножители в проекте пользователя возможно через мегафункции. Meгафункции lpm\_mult, altmult\_add и altmult\_accum позволяют умножители. Рассмотрим использовать аппаратные мегафункцию ALTMEMMULT – программный умножитель. ALTMEMMULT Мегафункция позволяет осуществлять процесс умножения числа на константу С, при этом константа может храниться в блочной памяти ПЛИС либо загружается с внешнего порта.

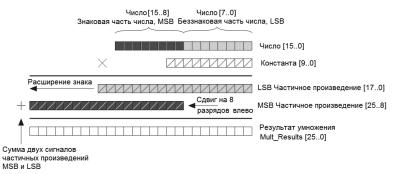

Для ПЛИС серии Cyclone II возможно использовать только память M4K (128х36 бит) или режим Avto. Например, ПЛИС EP2C70 содержит 250 блоков M4K. На рис. 1.35 показана идея умножения числа на константу. В целом,

принцип умножения, показанный на рис. 1.35, не отличается от ранее рассмотренного. При этом число и константа могут быть как со знаком, так и без него. На рис. 1.36 показан принцип построения программного умножителя 16-разрядного числа на 10-разрядную константу (обозначена буквой С) с использованием блоков памяти типа М4К большего размера, чем у БИС ПЛ фирмы Actel для случая, когда константы хранятся в блочной намяти, т.е. отсутствует возможность их загрузки извне (отсутствуют адресные порты для загрузки коэффициентов).

Рис. 1.35. Идея параллельного умножения 16-разрядного числа на 10-разрядную константу

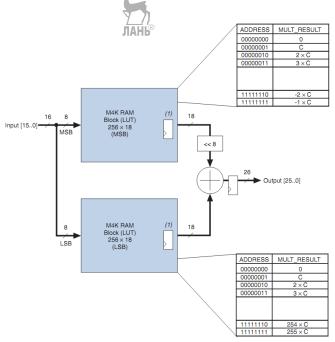

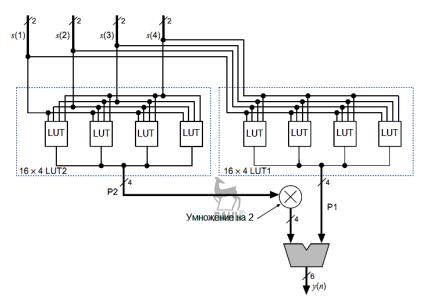

Входной 16-разрядный сигнал разделяется на два 8разрядных сигнала с именами LSB (младший значащий разряд) и MSB (старший значащий разряд). Сигнал LSB адресуется к блоку памяти M4K с одноименным названием LSB, а сигнал адресуется блоку памяти M4K К одноименным LSB названием MSB. В блочной хранятся 256 памяти предварительно вычисленных частичных произведений "LSB Частичное произведение [17..0]" частичное произведение) разрядностью 18 бит с диапазоном от 0 до 255xC, а в памяти MSB с диапазоном от 0 до (-1)xC 256 хранятся предварительно вычисленных частичных произведений с именем "MSB Частичное произведение [25..8]" (старшее частичное произведение). Далее старшее частичное произведение необходимо сдвинуть на восемь разрядов влево, а затем осуществить сквозное суммирование.

Рис. 1.36. Программный параллельный умножитель 16разрядного числа на 10-разрядную константу размерностью 16x10 с использованием двух блоков памяти типа M4K в качестве LUT фирмы Altera

Умножение фактически осуществляется за один такт синхроимпульса, необходимый для загрузки входных значений сигналов LSB и MSB в адресные порты блоков памяти. Еще два такта требуются для конвейеризации задержки вычислений, т.к. выходные значения блоков памяти, представляющие собой частичные произведения, должны быть

еще просуммированы с соответствующими весами для получения 26-разрядного результата умножения.

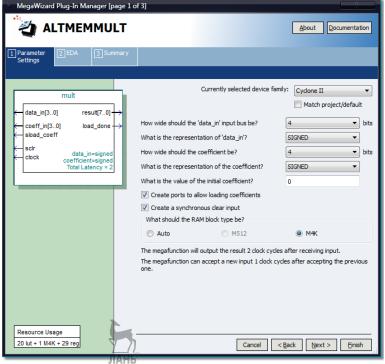

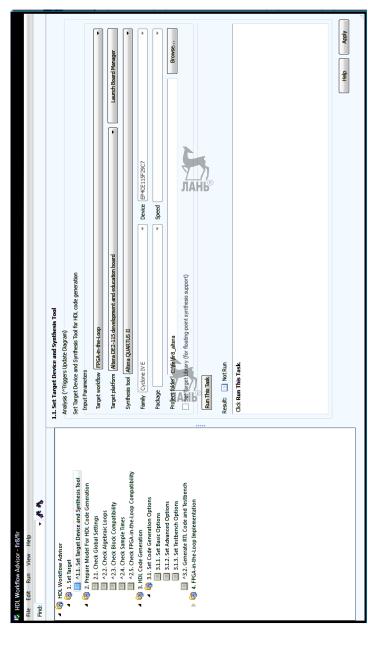

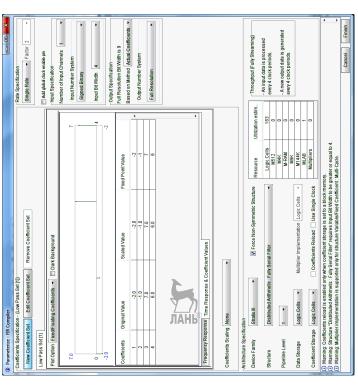

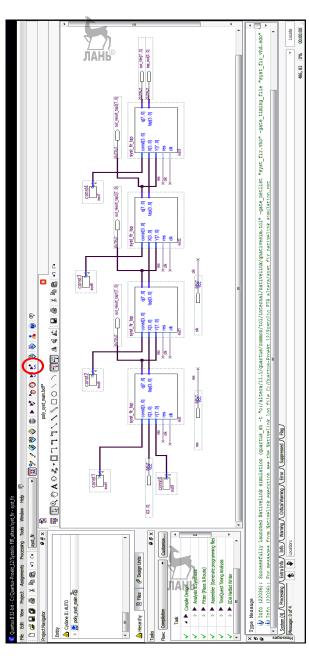

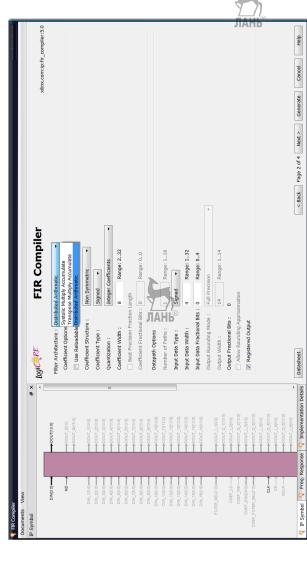

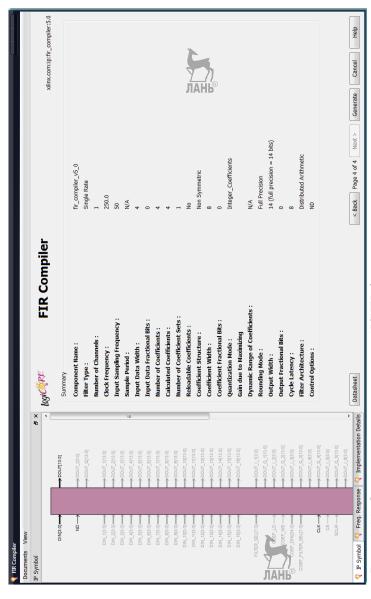

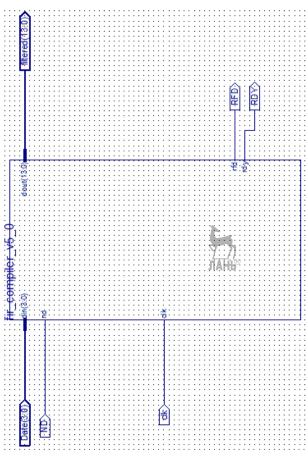

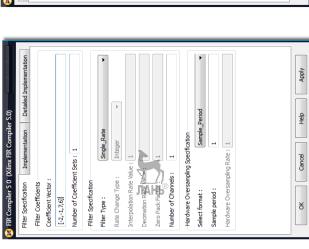

В качестве примера на рис. 1.37 показаны настройки мегафункции ALTMEMMULT для умножения 4-разрядного числа, представленного дополнительным кодом, и 4-разрядной константы, загружаемой из внешнего порта. В этом случае требуется 20 LUT логических блоков плюс 1 блок памяти типа M4K и 20 триггеров (20 lut+1M4K+20 reg). В случае загрузки константы из блочной памяти требуется всего лишь 1M4K.

Рис. 1.37. Мегафункция ALTMEMMULT, настроенная для реализации программного умножителя 4x4

Принцип построения на рис. 1.36 не раскрывает все тонкости такого умножителя. В частности, не показана

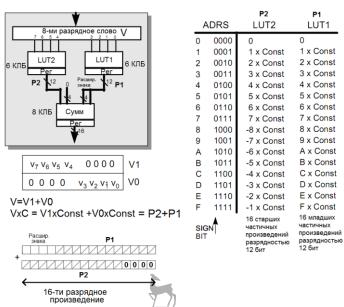

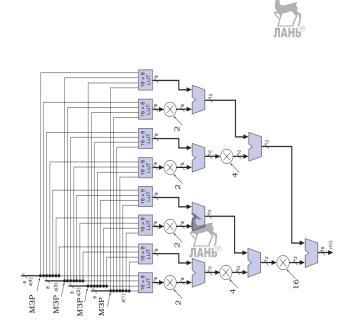

операция расширения знака числа. На рис. 1.38 показан принцип построения программного умножителя на константу размерностью 8х8 с использованием двух 4-входовых LUT ПЛИС серии XC4000. На рис. 1.38 обозначено: V - входной 8-разрядный сигнал; Р1 и Р2 - младшее и старшее частичные произведения; С - константа. В частности, показано, как на практике осуществляется сдвиг на четыре разряда влево. Для умножителя требуются 25 конфигурируемых логических блоков (КЛБ). Объединяя такие умножители в секции (одна фильтра), секция на отвод онжом построить КИХ-фильтр, высокопроизводительный параллельный работающий на частотах 50-70 МГц.

Рис. 1.38. Программный умножитель на константу размерностью 8x8 с использованием двух 4-входовых LUT ПЛИС серии XC4000

## 1.7. Разработка проекта умножителя размерностью 4х4 в базисе ПЛИС типа ППВМ серии Cyclone фирмы Altera с помощью учебного лабораторного стенда LESO2.1

В разделе 1.3 рассмотрено проектирование умножителя целых положительных чисел, представленных в прямом коде, размерностью 4х4 методом правого сдвига и сложения (МАС-блок), а в разделе 1.4 - проектирование умножителя целых чисел со знаком, представленных в дополнительном коде. В обоих случаях управляющие автоматы являлись оригинальными и были разработаны с использованием языка VHDL.

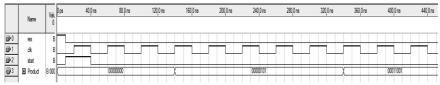

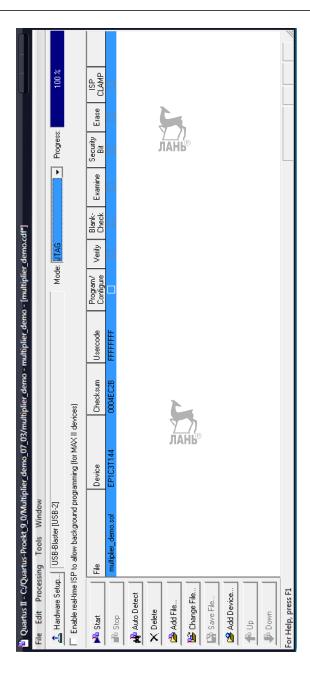

Рассмотрим проектирование цифрового автомата более простым способом - методом умножения в столбик. Управляющий автомат умножителя разработаем с помощью редактора состояний САПР Quartus II (State Machine Viewer). Далее реализуем умножитель размерностью 4х4 в базисе ПЛИС типа ППВМ серии Cyclone EP1C3T144C8N фирмы Altera с помощью учебного лабораторного стенда LESO2.1 (Лаборатории электронных средств обучения, ЛЭСО ГОУ ВПО «СибГУТИ») отечественной разработки. Учебный лабораторный стенд предназначен для обучения основам проектирования цифровой техники на основе ПЛИС.

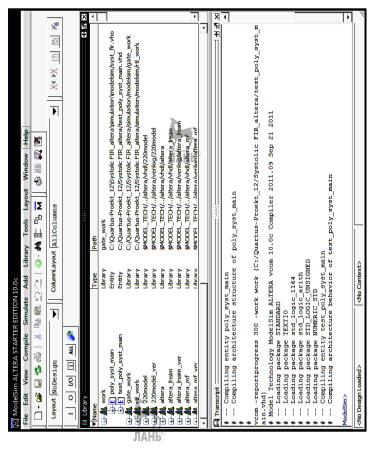

Так как САПР Quartus II Web Edition version 13.0.1 сборка 232 не поддерживает ПЛИС серии Cyclone, то необходимо перейти на более раннюю версию Quartus II Web Edition version 9.1.

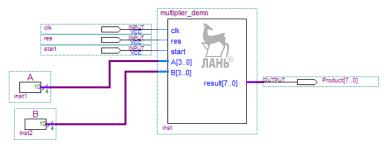

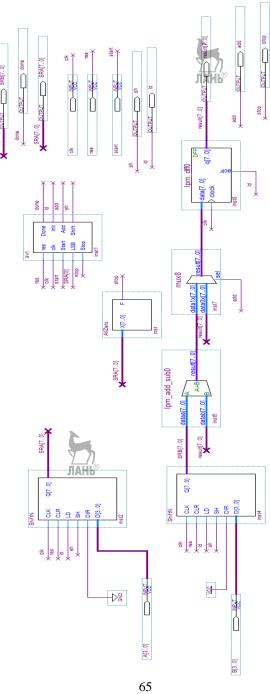

На рис. 1.39 и рис. 1.40 показаны верхний и нижний уровни иерархии проекта умножителя (P=B(множимое)\*A(множитель)) размерностью 4х4. Сигнал А (множитель) следует рассматривать как число, а сигнал В - как

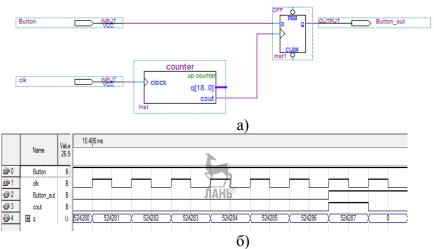

константу (множимое). Умножитель настроен на умножение двух чисел 10х10. Умножитель состоит из двух однотипных регистров ShiftN, сдвигающих влево или вправо в зависимости от сигнала DIR задающего направление сдвига (пример 1), детектора нуля AllZero, управляющего автомата avt на пять 2), состояний 8-разрядного (пример сумматора на мегафункции lpm\_add\_sub, шинного мультиплексора на мегафункции lpm\_mux 8-разрядного И регистра на мегафункции lpm\_dff, выполняющего роль аккумулятора. Один из регистров ShiftN (DIR=0), на вход которого подается число А, работает как преобразователь параллельного кода в последовательный, параллельный выход SRA[7..0] нужен лишь для детектирования нуля.

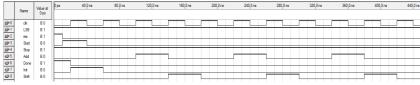

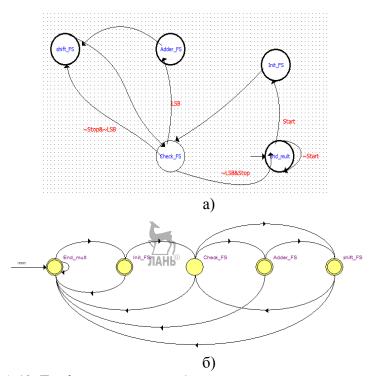

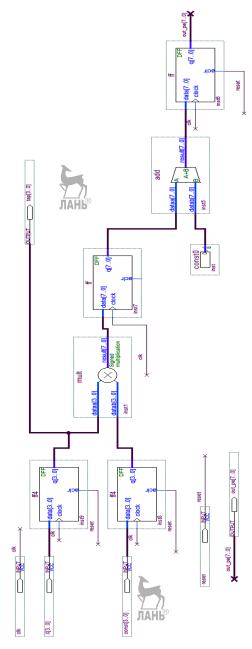

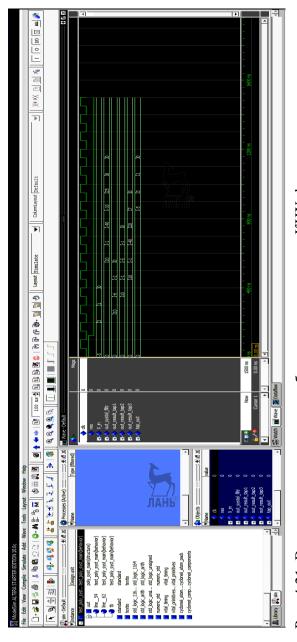

Рис. 1.41 демонстрирует принцип работы управляющего автомата. Автомат принимает пять состояний с именами Check\_FS, Init\_FS, Adder\_FS, shift\_FS, End\_mult. В каждом из состояний активным является один из сигналов Init, Add, Shift и Done. Автомат разработан по "классической" схеме с использованием одного оператора Process (однопроцессный шаблон) для описания памяти состояний и логики переходов.

Рис. 1.39. Умножитель размерностью 4х4. Верхний уровень иерархии

Рис. 1.40. Умножитель размерностью 4х4. Нижний уровень иерархии

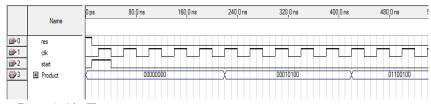

Автомат инициализируется высоким уровнем сигнала Start синхронизируемого синхросигналом clk, переводящим выход Init в активное состояние. При высоком уровне сигнала Init происходит загрузка обоих СДВИГОВЫХ регистров параллельным кодом. Если на вход LSB все время будет поступать логическая 1 (младший разряд SRA[0] 8-разрядного сигнала SRA[7..0]) с выхода сдвигового регистра ShiftN при DIR=0, то управляющий автомат будет вырабатывать сигналы "сложить" (Add) И "сдвинуть" (Shift). Это например, при загрузке числа 15D (1111BIN). На рис. 1.42 показан пример умножения чисел 10х10. Результат 100. По процесса умножения вырабатывается окончании готовности Done.

Рис. 1.41. Тест цифрового автомата

Рис. 1.42. Тестирование умножителя на примере умножения 10x10. Результат 100

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

entity ShiftN is

port(CLK, CLR, LD, SH, DIR: in STD_LOGIC;

D: in std_logic_vector(3 downto 0);

Q: out std_logic_vector(7 downto 0));

end ShiftN:

architecture a of ShiftN is

begin

process (CLR, CLK)

variable St: std logic vector(7 downto 0);

subtype InB is natural range 3 downto 0;

begin

if CLR = '1' then

St := (others => '0'); Q <= St;

elsif CLK'EVENT and CLK='1' then

if LD = '1' then

St:=(others=>'0');

St(InB) := D;

Q \leq St:

elsif SH = '1' then

case DIR is

when 0' \Rightarrow St := 0' \& St(St'LEFT downto 1);

when '1' => St := St(St'LEFT-1 \text{ downto } 0) \& '0';

end case;

Q \leq St;

end if:

end if:

end process;

end a:

Пример 1. Сдвиговый регистр на языке VHDL

```

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY avt IS

PORT (

res: IN STD_LOGIC;

clk: IN STD LOGIC;

Start: IN STD_LOGIC;

LSB: IN STD LOGIC;

Stop: IN STD LOGIC;

Done: OUT STD LOGIC;

Init: OUT STD LOGIC;

Add: OUT STD LOGIC:

Shift : OUT STD_LOGIC);

END avt:

ARCHITECTURE BEHAVIOR OF avt IS

TYPE type fstate IS (Check FS,Init FS,Adder FS,shift FS,End mult);

SIGNAL fstate: type fstate:

SIGNAL reg fstate: type fstate;

BEGIN

Init <='1' when reg fstate = Init FS else '0';

Add <='1' when reg_fstate = Adder_FS else '0';

Shift <='1' when reg fstate = shift FS else '0';

Done <='1' when reg fstate = End mult else '0';

process (clk, res) begin

if res = '1' then reg fstate <= End mult;

elsif clk'event and clk = '1' then

case reg fstate is

when Init_FS => reg_fstate <= Check_FS;

when Check FS =>

if LSBJAMP then reg fstate <= Adder FS;

elsif Stop ='0' then reg fstate <= shift FS;

else reg fstate <= End mult;

end if:

when Adder FS => reg fstate <= shift FS;

when shift FS => reg fstate <= Check FS;

when End_mult => if Start = '1' then reg_fstate <= Init_FS; end if;

end case:

end if:

end process;

END BEHAVIOR:

Пример 2. Код языка VHDL управляющего автомата

```

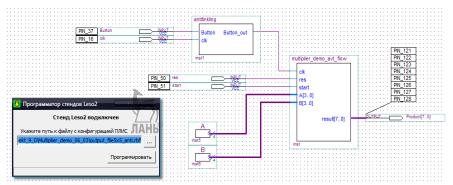

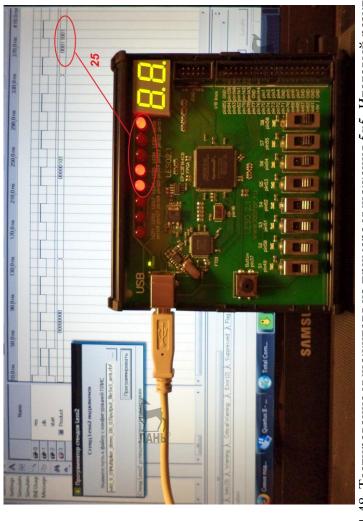

Разработаем цифровой автомат c использованием редактора состояний встроенного конечного автомата (рис. 1.43) и извлечем код языка VHDL в автоматическом режиме. Используется двухпроцессный шаблон. оператор Process описывает блок регистров (память состояний) для хранения состояний автомата. Второй оператор Process используется для описания логики переходов формирования выхода (пример 3). Тестирование умножителя на примере умножения 5х5 показано на рис. 1.44. Общие сведения по числу задействованных ресурсов в проекте показаны в табл. 1.4.

Рис. 1.43. Граф-автомат, разработанный с помощью редактора состояний (а) и синтезированный граф-автомат (меню Netlist Viewers/State Machine Viewer)

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY avt flow IS

PORT (

reset : IN STD_LOGIC := '0';

clock: IN STD_LOGIC;

Start: IN STD_LOGIC:= '0';

LSB : IN STD_LOGIC := '0';

Stop: IN STD LOGIC := '0';

Done: OUT STD LOGIC;

Init: OUT STD LOGIC;

Add: OUT STD LOGIC;

Shift: OUT STD LOGIC

);

END avt flow;

ARCHITECTURE BEHAVIOR OF avt flow IS

TYPE type fstate IS (Check FS,Init FS,Adder FS,shift FS,End mult);

SIGNAL fstate: type_fstate;

SIGNAL reg fstate: type fstate;

BEGIN

PROCESS (clock,reg_fstate)

BEGIN

IF (clock='1' AND clock'event) THEN

fstate <= reg fstate;

END IF:

END PROCESS;

PROCESS (fstate,reset,Start,LSB,Stop)

BEGIN

IF (reset='1') THEN

reg fstate <= End mult;

Done <= '0';

Init <= '0';

Add \le '0':

Shift <= '0':

ELSE

Done \leq 0';

Init <= '0';

Add \le 0;

70

Shift <= '0';

```

```

CASE fstate IS

WHEN Check FS =>

IF ((NOT((LSB = '1')) AND (Stop = '1'))) THEN

reg_fstate <= End_mult;

ELSIF ((LSB = '1')) THEN

reg fstate <= Adder FS;

ELSIF ((NOT((Stop = '1')) AND NOT((LSB = '1')))) THEN

reg_fstate <= shift_FS;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= Check_FS;

END IF;

WHEN Init FS =>

reg_fstate <= Check_FS;

Init <= '1';

WHEN Adder FS =

reg_fstate <= shift_FS;

Add <= '1';

WHEN shift_FS =>

reg fstate <= Check FS;

Shift <= '1';

WHEN End mult =>

IF ((Start = '1')) THEN

reg fstate <= Init FS;

ELSIF (NOT((Start = '1'))) THEN

reg fstate <= End mult;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= End_mult;</pre>

END IF;

Done <= '1';

```

WHEN OTHERS =>

Done <= 'X';

Init <= 'X';

Add <= 'X';

Shift <= 'X';

report "Reach undefined state";

END CASE;

END IF;

END PROCESS;

END BEHAVIOR;

Пример 3. VHDL-код, извлеченный в автоматическом режиме из граф-автомата, созданного с помощью редактора состояний в САПР Quartus II

Рис. 1.44. Тестирование умножителя на примере умножения 5x5. Результат 25

Таблица 1.4 Общие сведения по числу задействованных ресурсов ПЛИС Cyclone EP1C3T144C8N

| Логические    | Триггеры       | Таблицы       | Рабочая   |

|---------------|----------------|---------------|-----------|

| элементы      | логических     | перекодировок | частота в |

| (Logic Cells, | элементов      | (LUT-only LC) | наихудшем |

| ЛЭ)           | (LC Registers) |               | случае    |

|               |                |               | Fmax, МГц |

| 47            | 41             | 6             | 275       |

Стенд подключается к персональному компьютеру через порт USB. Для записи файла конфигурации в память ПЛИС через порт USB персонального компьютера требуется преобразовать \*.sof-файл в формат с расширением \*.rbf.

Загрузка конфигурационного файла в ПЛИС производится с помощью отдельной программы – загрузчика (12flash.exe).

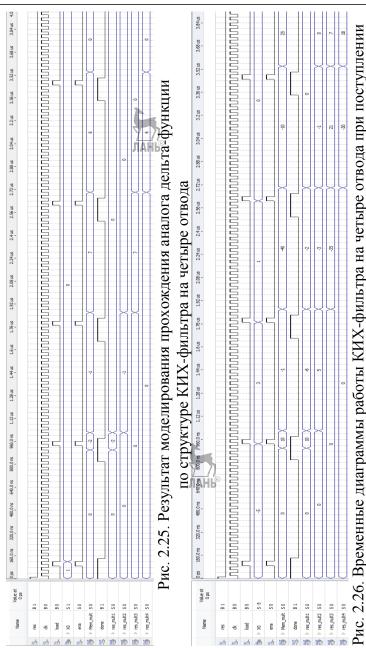

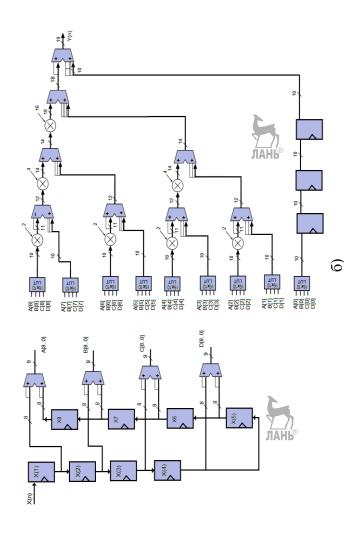

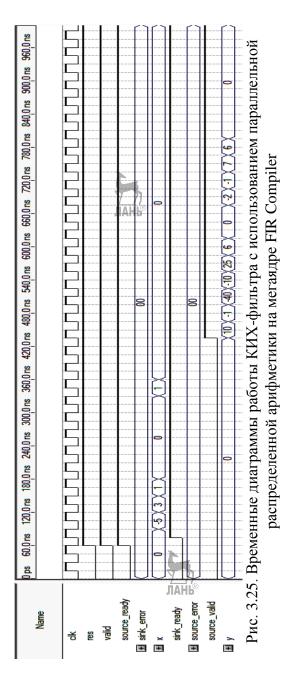

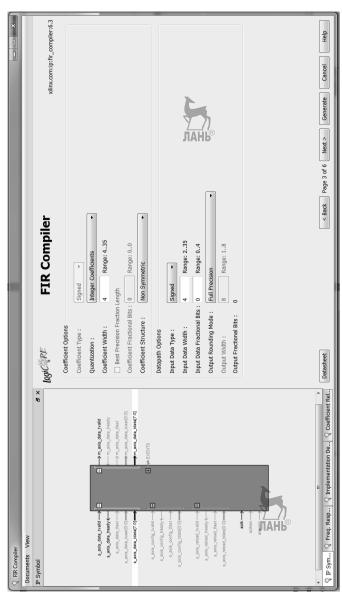

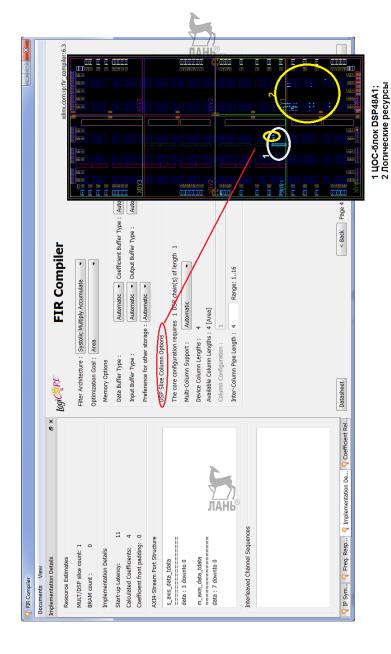

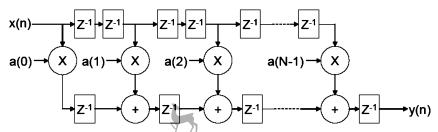

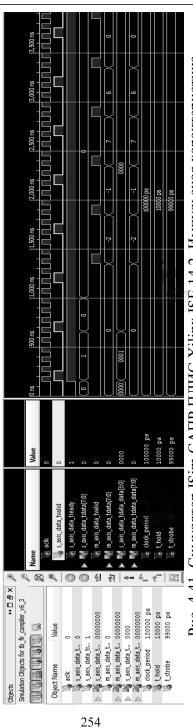

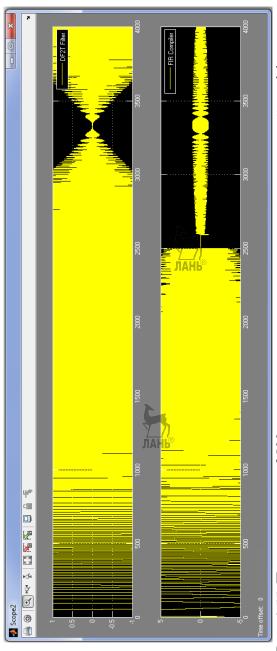

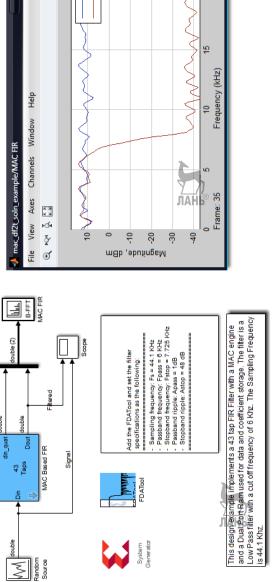

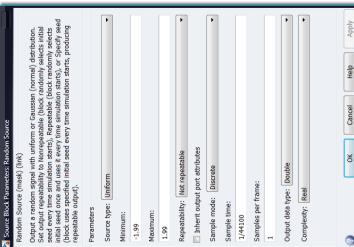

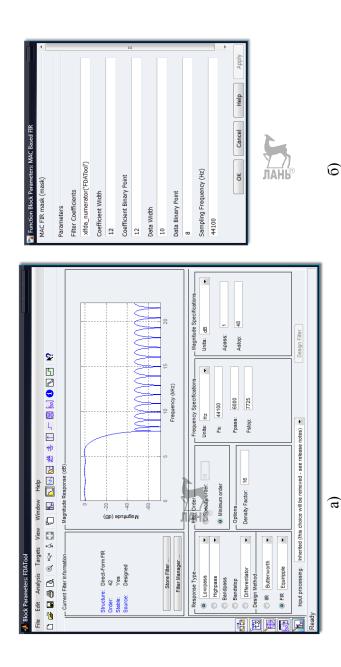

Входные и выходные контакты к внешним выводам ПЛИС подключены помощью Assignments/Pins c меню (рис. 1.45). Из-за того, что стенд имеет 8 переключателей S1-S8, пришлось отказаться от загрузки чисел с внешних портов (4-разрядные сигналы A и B) и от сигнала Done, так как доступно всего лишь 8 светодиодов. Умножаемые числа сохраняются константах (мегафункция предварительно В LPM constant). Далее необходимо следовать рис. 1.44 и 1.45. Светодиоды LED1-LED8 отображают результат умножения (8-разрядный сигнал Product[7..0]). В проекте принято, что LED8 (pin 121) - младший значащий разряд.